Overview

Description

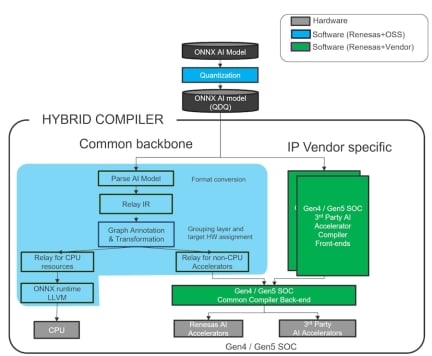

DNN compilers are often dedicated to each SoC, which is a high barrier to implementation for customers who design continuously across generations.

The DNN compiler is divided into a front-end part and a back-end part. The front-end part analyzes the graph structure of the neural network, compresses and optimizes the graph, while the back-end part determines the optimal order of operations based on the hardware structure and generates hardware instructions. However, our engineers’ design experience accumulated over many generations have found the front-end parts behave very similarly across all SoC generation.

To improve design efficiency and accelerate time-to-market, Renesas hybrid compiler (HyCo) uses the OSS TVM as a common backbone with excellent functionality extensions in the front-end and integrate the TVM with the back-end designed for each SoC, enabling developers to reuse the same tools across generations.

Features

- Hybrid Compiler

- Open-Source Software based AI compiler as common backbone

- IP vendor specific quality qualified AI compiler

Target Devices

Design & Development

Videos & Training

News & Blog Posts

| Explore the Cost-Effective Way to Support Mandatory ADAS Systems | Blog Post | Jul 26, 2024 |