Overview

Description

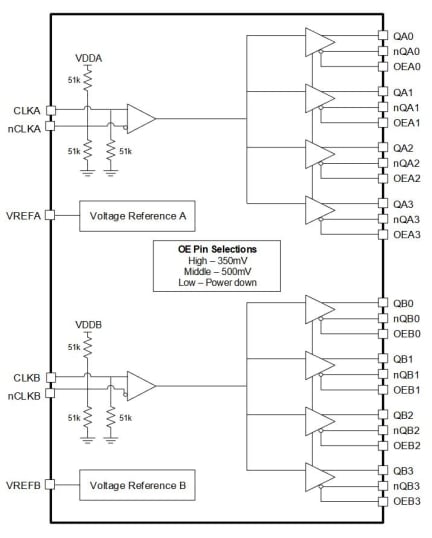

The 8P34S2104-1 is a differential dual 1:4 LVDS output 1.8V/2.5V fanout buffer that boasts high performance and low power consumption. It is engineered to support fail-safe operation and is specifically designed for the fanout of high-frequency clock and data signals with very low additive phase noise. The device comprises two independent buffer channels, and each of these channels has four outputs with low skew. High isolation between the channels ensures minimal noise coupling.

The 8P34S2104-1 excels in clock distribution applications that require well-defined performance and repeatability due to its guaranteed output-to-output and part-to-part skew characteristics. The device can operate using a 1.8V or 2.5V power supply. Its integrated bias voltage references allow for the easy interfacing of AC-coupled signals with the device's inputs.

The 8P34S2104-1 has the individual OE/Swing control pin for each output, which provides excellent control over both swing and output enable functions.

Features

- Dual 1:4 low skew, low additive jitter LVDS fanout buffers

- Individual OE/Swing control pin for each output

- Matched AC characteristics across both channels

- High isolation between channels

- Both differential CLKA, nCLKA and CLKB, nCLKB inputs accept LVDS, LVPECL, and single-ended LVCMOS levels

- Maximum input clock frequency: 2GHz

- Selectable output amplitudes: 350mV, 500mV or disable

- Output skew: 20ps typical

- Low additive phase jitter, RMS: 50fs typical

(fREF = 156.25MHz, 12kHz to 20MHz) - Full 1.8V and 2.5V supply voltage mode

- Low device current consumption (IDD): 230mA (typical)

- Lead-free (RoHS 6), 40-lead VFQFPN packaging

- -40 °C to +85 °C ambient operating temperature

- Supports case temperature up to +105 °C

Comparison

Applications

- 4G and 5G radio unit (RU) and distributed unit (DU) systems

- Ethernet switches/routers

- Medical imaging

- Professional audio and video

- Data centers and servers

Documentation

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 434 KB | |

1 item

|

||

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.