Overview

Description

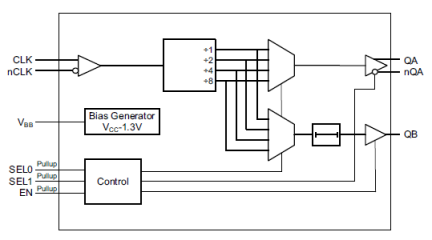

The 8T73S1802 is a fully integrated clock fanout buffer and frequency divider. The input signal is frequency-divided and then fanned out to one differential LVPECL and one LVCMOS output. Each of the outputs can select its individual divider value from the range of ÷1, ÷2, ÷4 and ÷8. Three control inputs EN, SEL0, and SEL1 (3-level logic) are available to select the frequency dividers and the output enable/disable state. The single-ended LVCMOS output is phase-delayed by 650ps to minimize coupling of LVCMOS switching into the differential output during its signal transition.

The 8T73S1802 is optimized to deliver very low phase noise clocks. The VBB output generates a common-mode voltage reference for the differential clock input so that connecting the VBB pin to an unused input (nCLK) enables to use of single-ended input signals. The extended temperature range supports wireless infrastructure, telecommunication, and networking end equipment requirements. The 8T73S1802 can be used with a 3.3V or a 2.5V power supply.

Features

- High-performance fanout buffer clock and fanout buffer

- Input clock signal is distributed to one LVPECL and one LVCMOS output

- Configurable output dividers for both LVPECL and LVCMOS outputs

- Supports clock frequencies up to 1000MHz (LVPECL) and up to 200MHz (LVCMOS)

- Flexible differential input supports LVPECL, LVDS, and CML

- VBB generator output supports single-ended input signal applications

- Optimized for low phase noise

- 650ps delay between LVCMOS and LVPECL minimizes coupling between outputs

- Supply voltage: 3.3V or 2.5V

- -40 °C to 85 °C ambient operating temperature

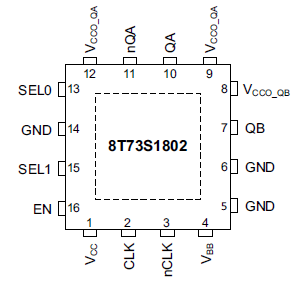

- 16 VFQFN package (3mm x 3mm)

Comparison

Applications

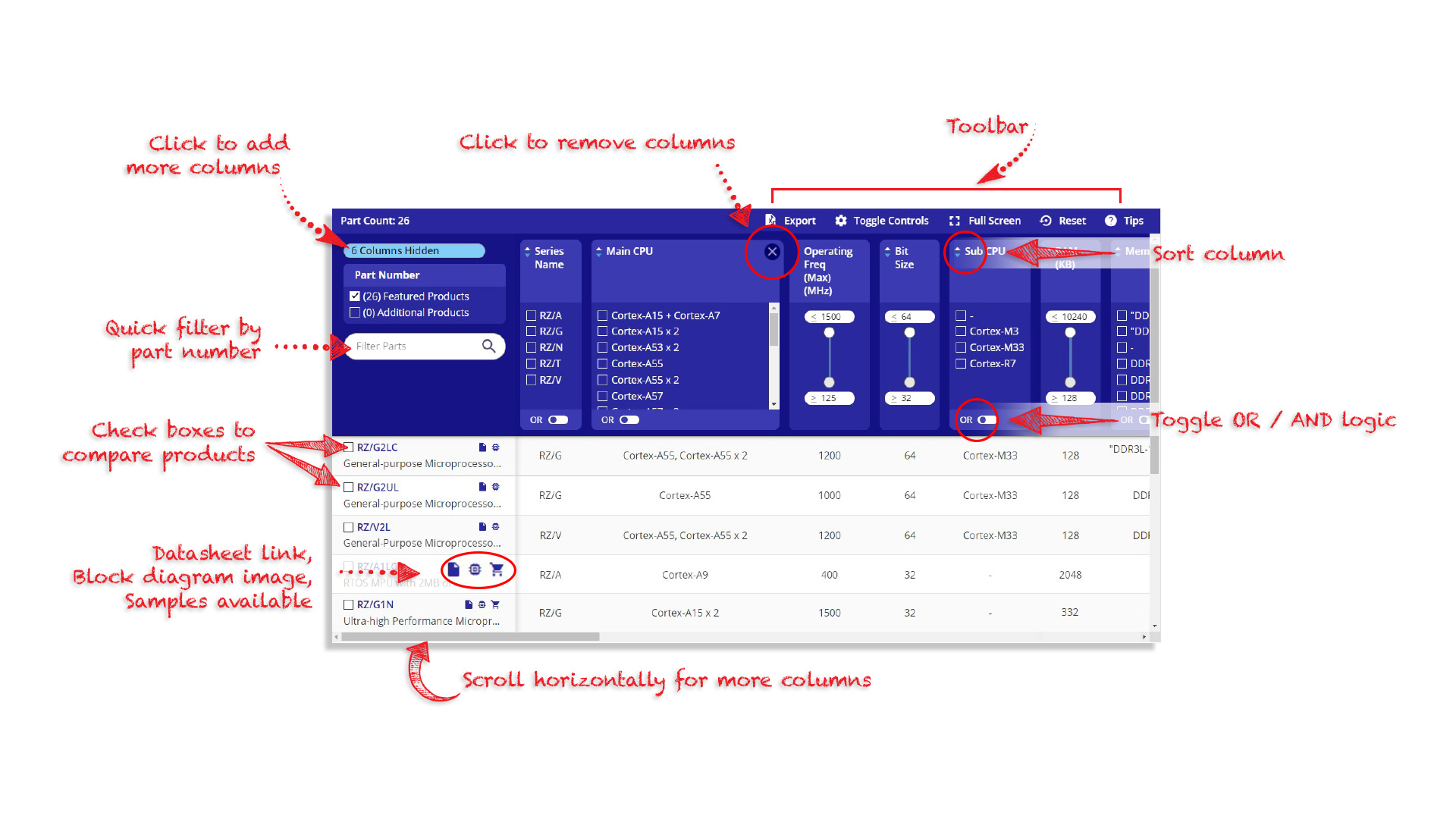

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.