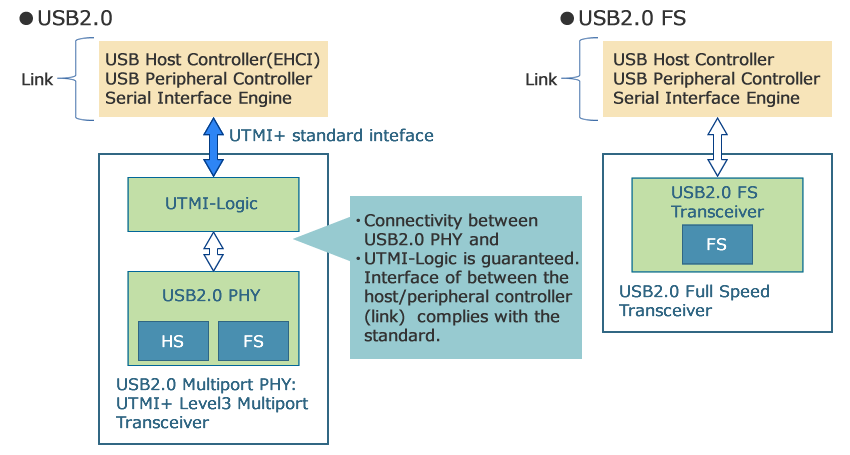

USB HS(2.0) / USB FS(1.1) PHY

By combining USB2.0 PHY and UTMI-Logic, we can provide an interface solution that complies with the standard interface specification(UTMI + Level 3). In addition, the USB2.0 FS Transceiver has configuration in which the IO Buffer for USB Full/Low Speed are cut out from the USB2.0 PHY, and USB2.0 FS solution with a small area can be realized.

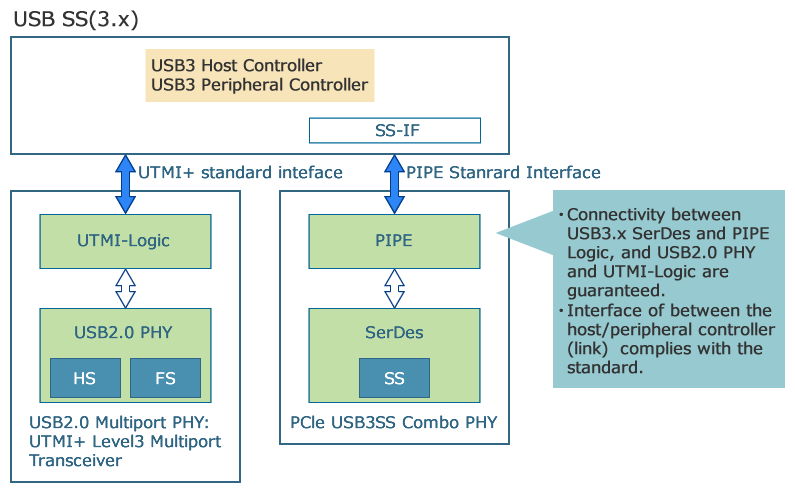

USB SS(3.x) PHY

By combining SerDes IP for USB SuperSpeed and PIPE Logic, and USB2.0 PHY and UTMI-Logic, we can provide an interface solution that complies with the standard interface specification(PIPE Interface, UTMI + Level 3).

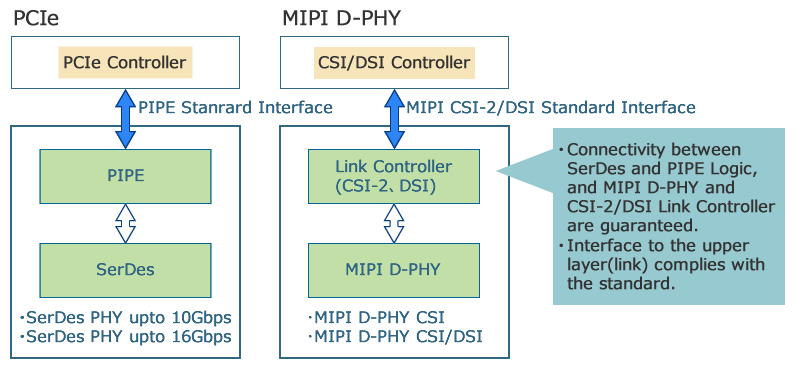

PCIe, MIPI D-PHY

By combining SerDes IP and PIPE Logic, we can provide an interface solution that complies with the PICe standard specification.

And By combining MIPI D-PHY and CSI-2/DSI Link Controller, we can provide an interface solution that complies with the MIPI CSI-2/DSI standard specification.