Overview

Description

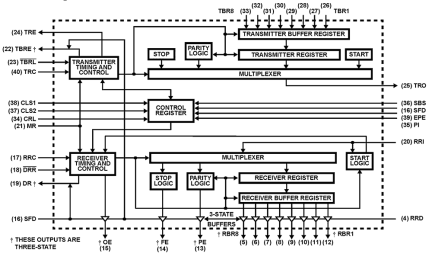

The HD-6402 is a CMOS UART for interfacing computers or microprocessors to an asynchronous serial data channel. The receiver converts serial start, data, parity and stop bits. The transmitter converts parallel data into serial form and automatically adds start, parity and stop bits. The data word length can be 5, 6, 7 or 8 bits. Parity may be odd or even. Parity checking and generation can be inhibited. The stop bits may be one or two or one and one-half when transmitting 5-bit code. The HD-6402 can be used in a wide range of applications including modems, printers, peripherals and remote data acquisition systems. Utilizing the Intersil advanced scaled SAJI IV CMOS process permits operation clock frequencies up to 8. 0MHz (500K Baud). Power requirements, by comparison, are reduced from 300mW to 10mW. Status logic increases flexibility and simplifies the user interface.

Features

- 8.0MHz Operating Frequency (5962-9052502)

- 2.0MHz Operating Frequency (HD3-6402R)

- Low Power CMOS Design

- Programmable Word Length, Stop Bits and Parity

- Automatic Data Formatting and Status Generation

- Compatible with Industry Standard UARTs

- Single +5V Power Supply

- CMOS/TTL Compatible Inputs

- Pb-Free Plus Anneal Available (RoHS Compliant)

Comparison

Applications

Documentation

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 322 KB | |

| Brochure | PDF 467 KB | |

| Product Change Notice | PDF 323 KB | |

| Product Advisory | PDF 282 KB | |

| Product Change Notice | PDF 174 KB | |

| Product Change Notice | PDF 151 KB | |

| Application Note | PDF 224 KB | |

7 items

|

||

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Applied Filters: