The growth in wireless systems infrastructure and the number of wireless devices deployed continues to grow year-on-year. Our insatiable desire for on-demand data and information – wherever and whenever – continues to challenge system requirements. Developments in 5G are happening quickly, as are increases in the number of satellites planned to enable all of this.

To provide end users with quicker access, guaranteed connectivity, and batteries with longer lifetimes, development of these RF communication systems is becoming more complex.

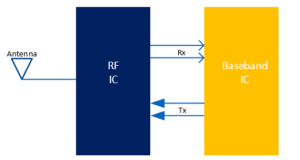

Despite new demands on these communication systems, at a top level, such systems have not changed too much over time. There is an antenna to connect the radio waves with the transceiver RF chip. In the receive path, the signal is filtered and amplified to separate the desired RF signal from the other signals picked up by the antenna, and the signal is then down-converted to the baseband frequencies. After being up-converted, the signal in the transmitter path is also filtered and amplified to drive the antenna. Typically, the data converters in the baseband chip act as the interface between the analog signals at the RF chip and the digital data processing.

Figure1: RF Communications Transceiver

In previous blogs, we have looked at various ADC architectures, but there are other considerations for broadband communications ADC design. What are they, and how do they translate into custom ASICs?

When considering broadband communications, we are looking at ADCs that have sampling rates of Giga-Samples Per Second (GSPS). Previously discussed architectures like the successive approximation register (SAR) ADC and the SAR-assisted pipeline ADC typically cannot achieve these rates. However, by combining the SAR-assisted pipeline ADC core with a time-interleaved architecture, it is possible to extend the sampling rate to GSPS, while also achieving a robust, low-power and highly efficient solution.

A time-interleaved ADC, sampling at Fs (frequency sampling) is implemented with a number M of sub-ADC cores, each one sampling sequentially at Fs/M. Each sub-ADC operates at M-times lower frequency which subsequently relaxes the design requirements and makes it easier to achieve the high frequency. However, each sub-ADC must be well matched with no delays in sampling time, and this is difficult to achieve. There are many sources of errors that can all cause degradation in the overall dynamic performance. As a result, calibration is used to remove these errors and improve the performance.

When converting broadband signals with time-interleaved ADCs, an accurate and efficient conversion is only possible with optimized and robust calibration. Performance, cost, and power all depend on the quality of this calibration.

Our designers have developed a number of custom ASICs in the broadband communications arena. The first was an ASIC for a fixed wireless access (FWA) application. FWA provides broadband communications between fixed locations via radio link rather than the traditional fiber or copper wire installation. The ASIC provided the baseband interface IC functionality, connecting the RF transceiver IC and the baseband processor IC. It included quadrature current steering digital-to-analog converters (DAC) and a quadrature SAR-assisted pipeline ADC. This ADC architecture was the perfect fit to minimize system complexity and costs.

The second ASIC was for G.fast communications. G.fast is an ultra-fast broadband technology that can achieve download speeds of over 100Mb/s while using the existing copper infrastructure. The ASIC solution we developed for this application was an analog front end (AFE) comprised of several components. Central to its functionality was a time-interleaved ADC and a current-steering DAC. The data converters sample the signal at 424MSps with performance of 52dB MTPR (multi-tone power ratio).

Regardless of the medium used to deliver wireless or wired broadband, the goals are increased coverage and capacity, and achieving these goals requires higher sample rate data converters. Time interleaved ADCs and SAR-assisted pipeline ADCs provide the data rates needed to service these requirements. With future demands for 5G needing data rates faster than 1Gb/s, we will continue to be at the forefront, developing the data converters needed to support your design or for integration by us into a custom ASIC. Learn more about our broadband communications technology.