Overview

Description

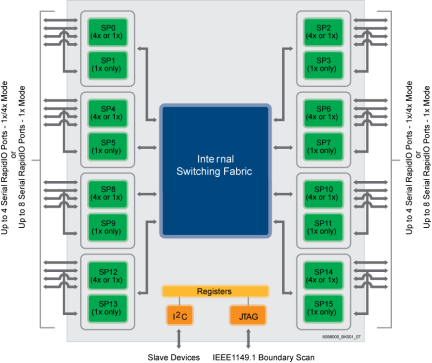

The IDT Tsi568A is a second-generation RapidIO switch. Supporting 80 Gbps aggregate bandwidth, the Tsi568 enables customers to develop high performance systems at low cost. The Tsi568A can be configured as a 16-port x1 switch or an 8-port x4 switch (or various combinations of x1 and x4). Each of the ports can be run at 1.25 Gbaud, 2.5 Gbaud, or 3.125 Gbaud. The Tsi568 is targeted at the following: Chip-to-chip DSP and processor aggregation Board-to-board backplane interconnect Chassis-to-chassis interconnect over copper or optics The Tsi568A supports open architectural standards such as AdvancedTCA and VITA VXS.

Features

- Bandwidth of up to 80 Gbps full duplex

- Low latency with cut-through capability

- Individual port power down

- RapidIO Interconnect Specification

- (Revision 1.2) compliant

Comparison

Applications

Design & Development

Software & Tools

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Videos & Training

Description

Transcript