Overview

Description

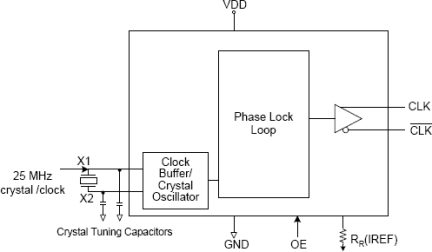

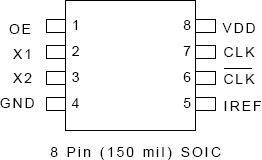

The 557-01 is a clock chip designed for use in PCI Express® cards as a clock source. It provides a pair of differential outputs at 100MHz in a small 8-pin SOIC package. Using Renesas' patented Phase-Locked Loop (PLL) techniques, the device takes a 25MHz crystal input and produces HCSL (Host Clock Signal Level) differential outputs at 100MHz clock frequency. LVDS signal levels can also be supported via an alternative termination scheme.

Features

- Supports PCI Express®TM HCSL Outputs 0.7V current mode differential pair

- Supports LVDS output Levels

- Packaged in 8-pin SOIC

- RoHS 5 (green) or RoHS 6 (green and lead-free) compliant packaging

- Operating voltage of 3.3V

- Low power consumption

- Input frequency of 25MHz

- Short-term jitter 100ps (peak-to-peak)

- Output Enable via pin selection

- Industrial temperature range available

- For PCIe Gen2 applications, see the 5V41064

- For PCIe Gen3 applications, see the 5V41234

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Applied Filters:

Videos & Training

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

Watch the Video Series Below