Evaluation Board Kit for RZ/T2H

The Evaluation Board Kit for RZ/T2H is an evaluation and development kit for the RZ/T2H MPU. Since it has an on-board emulator, you can start evaluation by simply...

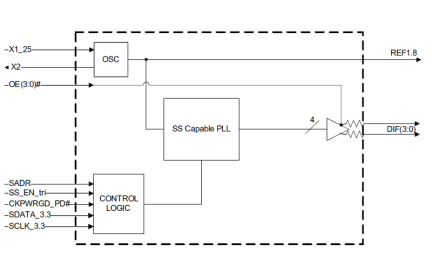

The 9FGV0441 is a 4-output very-low power clock generator for PCIe Gen 1–4 applications with integrated output terminations providing Zo = 100Ω. The device has four output enables for clock management and supports two different spread spectrum levels in addition to spread off.

The Evaluation Board Kit for RZ/T2H is an evaluation and development kit for the RZ/T2H MPU. Since it has an on-board emulator, you can start evaluation by simply...

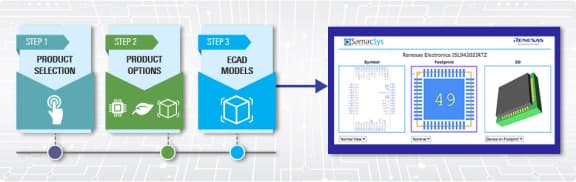

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Pkg. Type |

Lead Count (#) |

Temp. Grade |

Pb (Lead) Free |

Carrier Type |

Moisture Sensitivity Level (MSL) |

Price (USD) | 1ku |

Buy / Sample |

|

|---|---|---|---|---|---|---|---|---|

| Part Number | ||||||||

9FGV0441AKILF circleActive Samples Available

shopping_cart

Buy Now

|

VFQFPN | 32 | I | Yes | Tray | 3 | 1.951 | Get Samples, |

| VFQFPN | 32 | I | Yes | Reel | 3 | |||

9FGV0441AKLF circleActive Samples Available

shopping_cart

Buy Now

|

VFQFPN | 32 | C | Yes | Tray | 3 | 1.562 | Get Samples, |

| VFQFPN | 32 | C | Yes | Reel | 3 |

Ron Wade, chief PCIe system architect explains the fundamental difference in reference clock jitter budgets between the first three generations of the specification and those of Gen4 and Gen5 which raise new challenges for designers.

Related Resources