Overview

Description

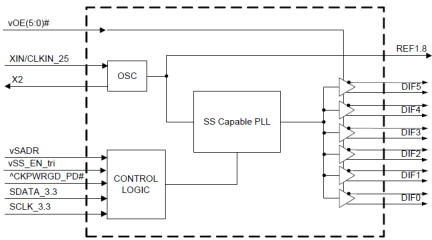

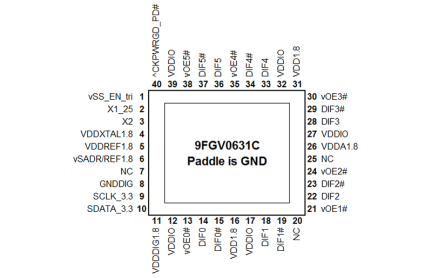

The 9FGV0631 is a member of IDT's SOC-Friendly 1.8 V Very-Low-Power PCIe clock family. The device has 6 output enables for clock management, 2 different spread spectrum levels in addition to spread off and 2 selectable SMBus addresses.

Features

-

PCIe Gen1–4 compliant

-

LP-HCSL outputs; save 12 resistors compared to standard PCIe devices

-

54 mW typical power consumption; reduced thermal concerns

-

Outputs can optionally be supplied from any voltage between 1.05 and 1.8 V; maximum power savings

-

OE# pins; support DIF power management

-

Programmable slew rate for each output; allows tuning for various line lengths

-

Programmable output amplitude; allows tuning for various application environments

-

DIF outputs blocked until PLL is locked; clean system start-up

-

Selectable 0%, -0.25% or -0.5% spread on DIF outputs; reduces EMI

-

External 25 MHz crystal; supports tight ppm with 0 ppm synthesis error

-

Configuration can be accomplished with strapping pins; SMBus interface not required for device control

-

3.3 V tolerant SMBus interface works with legacy controllers

-

Space saving 5x5 mm 40-pin VFQFPN; minimal board space

-

Selectable SMBus addresses; multiple devices can easily share an SMBus segment

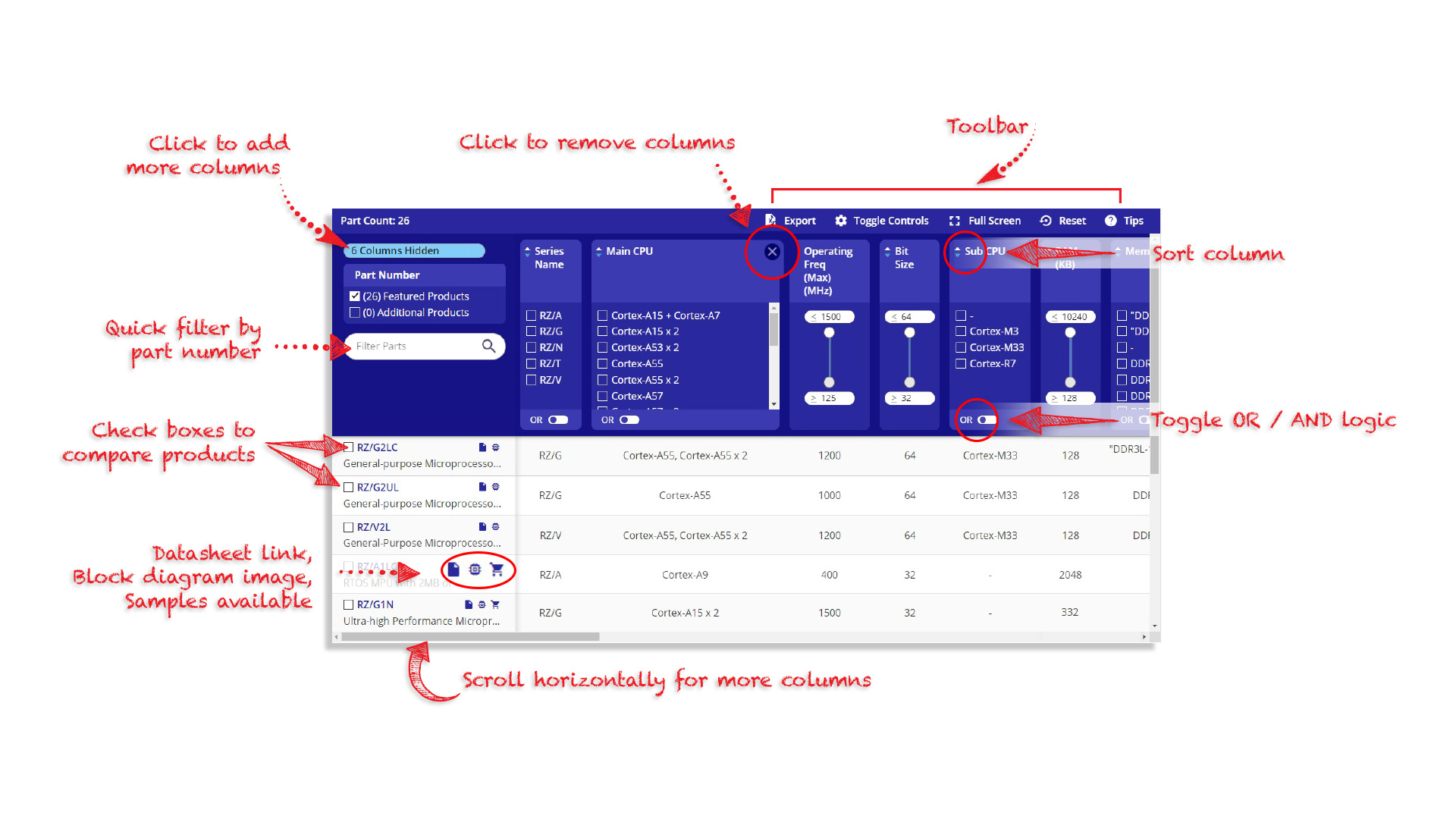

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Videos & Training

PCIe Reference Clock Jitter Budgets

Ron Wade, chief PCIe system architect explains the fundamental difference in reference clock jitter budgets between the first three generations of the specification and those of Gen4 and Gen5 which raise new challenges for designers.

Related Resources

Video List