Overview

Description

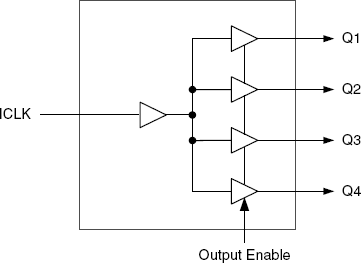

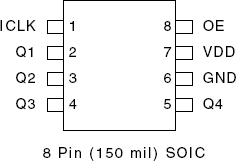

The 551 is a low cost, high-speed single input to four output clock buffer. Part of Renesas' ClockBlocksTM family, this is our lowest cost, small clock buffer. See the 552-02B for monolithic dual version of the 551 in a 20 pin QSOP. IDT makes many non-PLL and PLL based low skew output devices as well as Zero Delay Buffers to synchronize clocks. Contact Renesas for all of your clocking needs.

Features

- Low skew (250 ps) outputs

- Pb-free packaging

- Low cost clock buffer

- Packaged in 8-pin SOIC

- Input/Output clock frequency up to 160 MHz

- Non-inverting output clock

- Ideal for networking clocks

- Operating Voltages of 3.3 and 5.0 V

- Output Enable mode tri-states outputs

- Advanced, low power CMOS process

- Commercial and industrial temperature versions

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Applied Filters: