Overview

Description

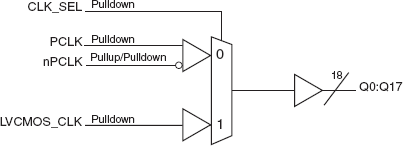

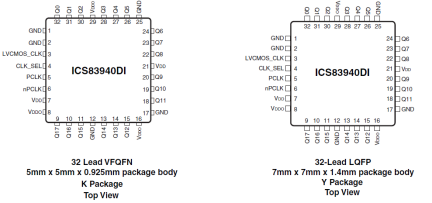

The 83940DI is a low skew, 1-to-18 LVPECL- to-LVCMOS/LVTTL Fanout Buffer. The 83940DI has two selectable clock inputs. The PCLK, nPCLK pair can accept LVPECL, CML, or SSTL input levels. The LVCMOS_CLK can accept LVCMOS or LVTTL input levels. The low impedance LVCMOS/LVTTL outputs are designed to drive 50Ω series or parallel terminated transmission lines. The 83940DI is characterized at full 3.3V and 2.5V or mixed 3.3V core, 2.5V output operating supply modes. Guaranteed output and part-to-part skew characteristics make the 83940DI ideal for those clock distribution applications demanding well defined performance and repeatability.

Features

- Eighteen LVCMOS/LVTTL outputs

- Selectable LVCMOS_CLK or LVPECL clock inputs

- PCLK, nPCLK pair can accept the following differential input levels: LVPECL, CML, SSTL

- LVCMOS_CLK supports the following input types: LVCMOS or LVTTL

- Maximum output frequency: 250MHz

- Output skew: 150ps (maximum)

- Part-to-part skew: 750ps (maximum)

- Operating supply modes:

Core/Output

3.3V/3.3V

3.3V/2.5V

2.5V/2.5V - -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

Comparison

Applications

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Applied Filters: