Overview

Description

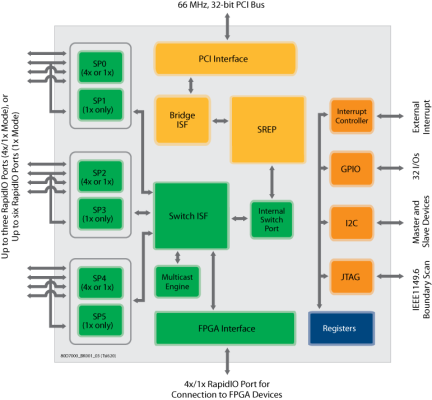

The IDT Tsi620 provides the functionality of both a RapidIO switch and a non-transparent RapidIO-to-PCI bridge. The RapidIO switch offers 50 Gbps aggregate bandwidth, while the RapidIO-to-PCI bridge enables legacy systems to link to the high-bandwidth RapidIO interconnect. The Tsi620 contains all the benefits of the IDT RapidIO Tsi switch family and adds interfaces to PCI-enabled processors, as well as an interface to low-cost FPGAs using a XGMII interface for the physical layer that transmits RapidIO at the logical layer at up to 10 Gbps.

Learn more: IDT RapidIO Development Systems

Features

- RapidIO Interface with configurable port modes

- Up to three ports in 4x modeUp to six ports in 1x mode (each 4x port can be configured independently as two 1x ports)FPGA Interface that supports one 4x or 1x RapidIO portPCI Interface

- 32/64-bit addressing, 32-bit dataUp to 66-MHz operation50 Gbps aggregate bandwidthLow latency with cut-through capabilityEnhanced Serializer/Deserializer (SerDes) for low-power solutionRapidIO Interconnect Specification (Revision 1.3) compliantHigh-performance Multicast EngineLow power

- Leverages Tsi57x technology at 120-200mW per RapidIO portTypical power at full operation is less than 4WSoftware compatibility

- RapidIO-to-PCI bridge software compatible with the Tsi108, Tsi109, and Tsi110RapidIO Switch software compatible with Tsi57x products

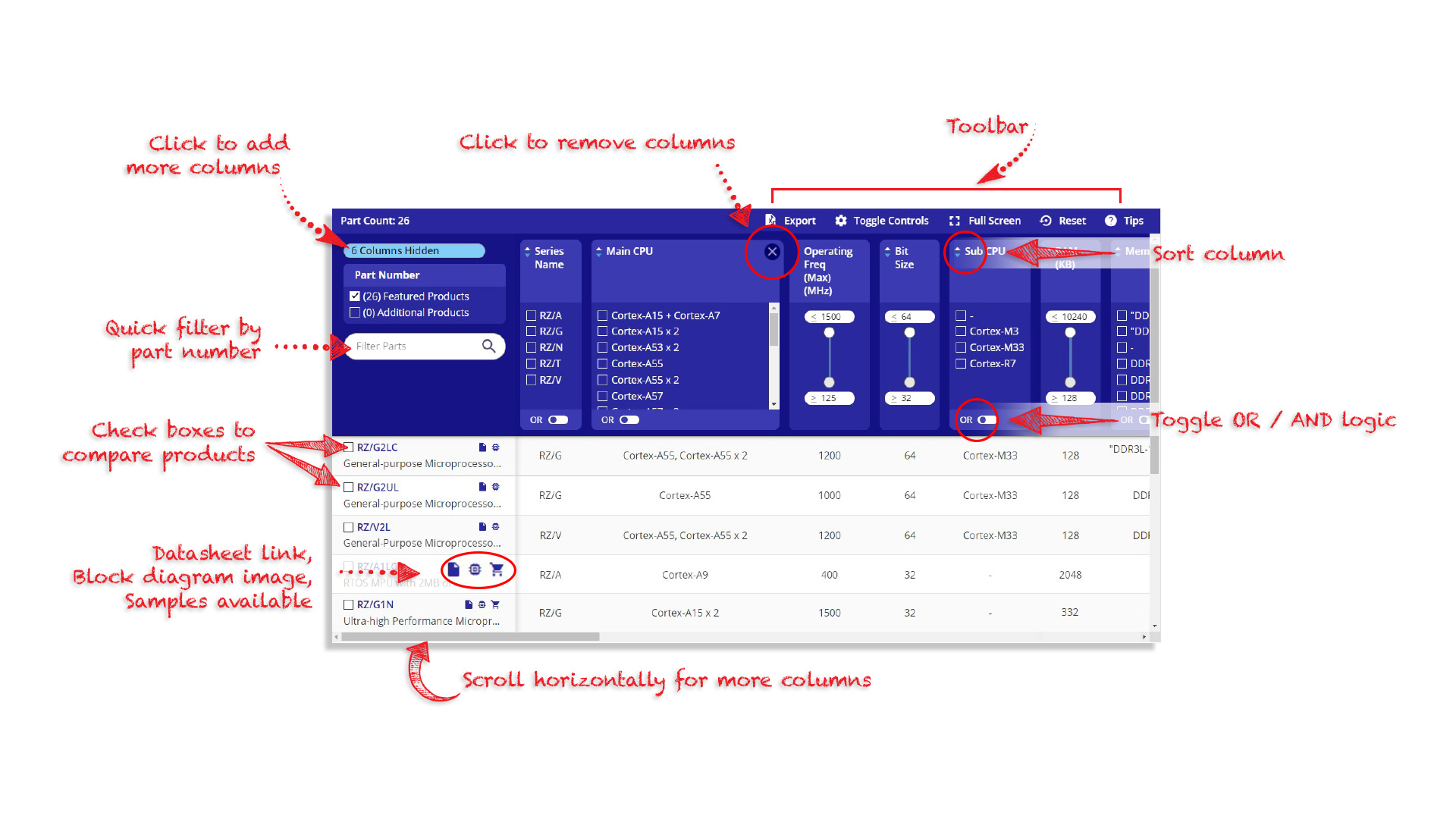

Comparison

Applications

Design & Development

Software & Tools

Models

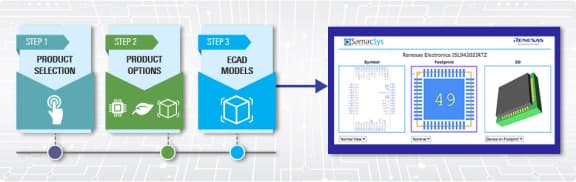

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Videos & Training

Description

Transcript