Evaluation Boards & Kits

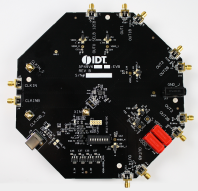

Evaluation Board for 5P49V60 Automotive VersaClock 6E

This is the evaluation board for the 5P49V60 automotive VersaClock® 6E programmable clock generator. With RMS phase jitter of less than 0.5ps over the full 12kHz to 20MHz integration range, the device meets the stringent jitter requirements of PCI Express® Gen 1–3, USB 3.0, and 1G/10G Ethernet.

R-Car V4H System Evaluation Board Set/White Hawk

The White Hawk is an R-Car V4H-specific evaluation board set that can be used to evaluate systems using the R-Car V4H and to develop operating systems, device drivers, and applications. Using the White Hawk board set allows the developers to efficiently conduct required tasks such as evaluation... Read More

High-End Cockpit & Infotainment Solution R-Car H3, M3 Development Board / Salvator-XS

The combination of R-Car (H3/M3/M3N) system in package (SiP) and Clock Generators delivers high efficiency while supporting a wide range of display outputs and high-quality performance, making it ideal for scalable cockpit and infotainment solutions.