Overview

Description

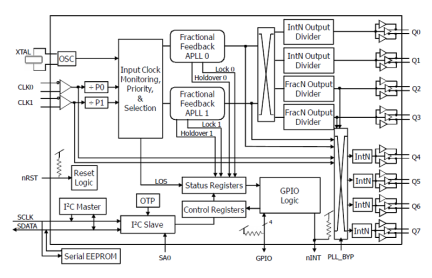

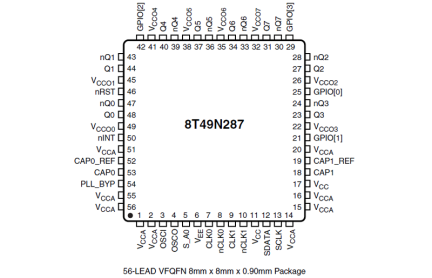

The 8T49N287 has two fractional feedback PLL’s that can be used as a frequency translators with jitter attenuation or a frequency synthesizers. It is equipped with six integer and two fractional output dividers, allowing the generation of up to eight different output frequencies, ranging from 8 kHz to 1 GHz. Output frequencies can be completely independent of the input frequencies, and up to four of these frequencies can be completely independent of each other. The eight outputs may select among LVPECL, LVDS, HCSL or LVCMOS output levels.

The 8T49N287 is ideal for use in a wide range of equipment, including 10G/40G/100G SONET/SDH and Ethernet network line cards, wireless base station baseband units, broadcast video, carrier Ethernet switches, OTN, or on test and measurement applications. The 8T49N287 can be used in GbE/10GbE/100GbE Synchronous Ethernet line card applications in order to preserve the G.8262 compliance from the Synchronous Equipment Timing Source (SETS) on the timing card.

Renesas’ third generation Universal Frequency Translator family also includes the 8T49N285 (2-in / 1-PLL / 8-out), 8T49N286 (4-in / 2-PLL / 8-out), and the 8T49N242 (2-in / 1-PLL / 4-out). These devices are complemented by the 82P33714 and 82P33731 synchronous equipment timing source (SETS) for Synchronous Ethernet (SyncE) and 10G-40G SyncE, respectively.

To see other devices in this product family, visit the Universal Frequency Translators page.

Features

- Supports GR.1244 Stratum 3 stability in holdover mode

- Compliant with the requirements outlined in Telcordia GR-253-CORE (SONET) & ITU-T G.813/G.8262 (SDH/SONET & SyncE) when paired with a Synchronous Equipment Timing Source (SETS ) device

- Generates up to 8 LVPECL / LVDS/HCSL or 16 LVCMOS output clocks ranging from 8kHz up to 1.0 GHz (diff), 8 kHz to 250 MHz (LVCMOS), that meet jitter limits for 10G up to 100G Ethernet and STM-256/OC-768 applications

- 0.3ps RMS (including spurs), 12 kHz to 20 MHz

- Accepts up to two LVPECL, LVDS, LVHSTL, HCSL or LVCMOS input clocks ranging from 8 kHz up to 875 MHz

- Auto and manual input clock selection with hitless switching

- Clock input monitoring, including support for gapped clocks

- Phase-Slope Limiting and Fully Hitless Switching options to control output phase transients

- Operates from a 10 MHz to 40 MHz fundamental-mode crystal

- Register programmable through I2C / SPI or via external I2C EEPROM

- 8T49N287-993 “Boot from EEPROM”

- 8T49N287-994 “powers up disabled”

- Supported by Timing Commander Software

Comparison

Applications

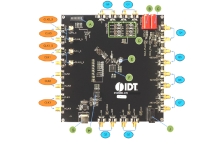

Design & Development

Software & Tools

Software & Tools

| Software title

|

Software type

|

Company

|

|---|---|---|

| Timing Commander Timing Commander™ is an innovative Windows™-based software platform enabling system design engineers to configure, program, and monitor sophisticated timing devices with an intuitive and flexible graphical user interface (GUI).

|

Code Generator | Renesas |

1 item

|

||

Boards & Kits

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Applied Filters:

Videos & Training

Description

Transcript

News & Blog Posts

| Benefits of a Point-of-Use Clock for Jitter Optimization | Blog Post | Apr 27, 2021 |