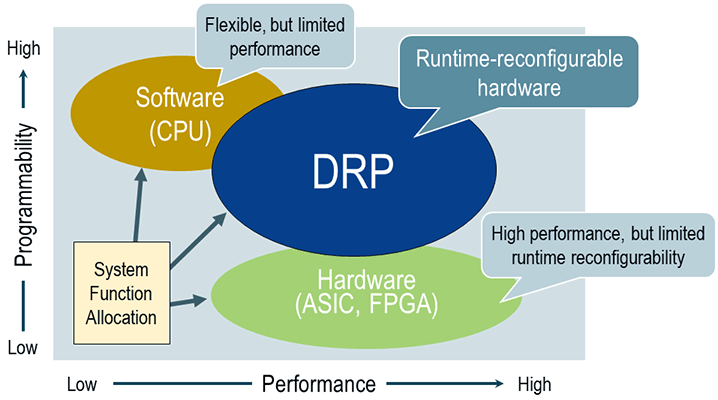

The Dynamically Reconfigurable Processor (DRP) technology from Renesas is special purpose hardware built into select RZ Family microprocessor units (MPUs) that dramatically accelerates image processing algorithms by as much as 10X, or more. It combines the high performance of hardware solutions with the flexibility and expansion capability of a CPU.

Additional DRP Information

Dynamically Reconfigurable Processor (DRP) Features & Advantages

Accelerator Type DRP

Dynamically Reconfigurable Processor (DRP) Technology Development

RZ/A2M MPUs with DRP

e-AI Solutions from Renesas

DRP Applications

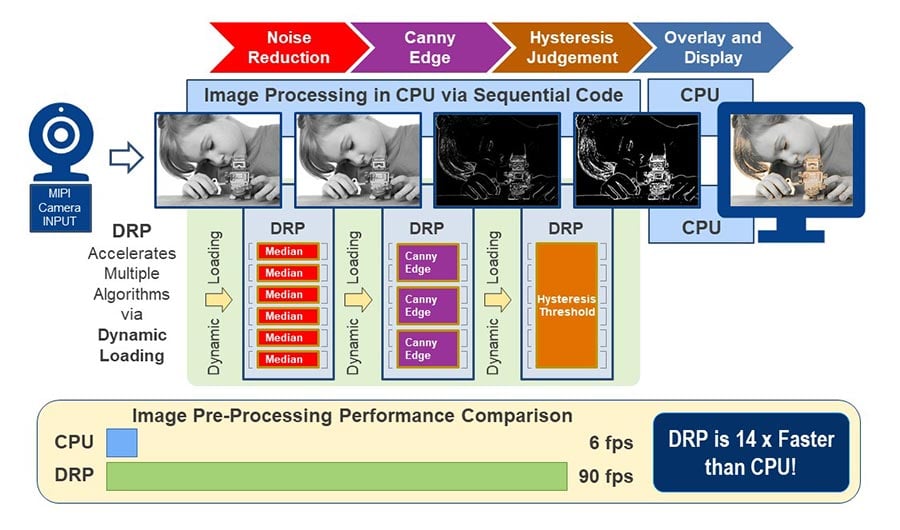

DRP technology is ideal for image processing acceleration where it can dramatically reduce processing time by pre-processing images to reduce workload on the CPU. Examples of this image processing acceleration include 2-D barcode scanning and iris detection and extraction.

DRP Technology Advantages

Flexibility

- The DRP can accelerate multiple algorithms in a single application and offload the main processor for specialized tasks

- New configurations can be dynamically loaded into the DRP in as little as 1ms

Programming

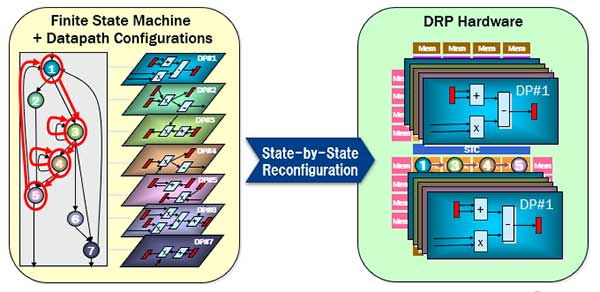

- Renesas creates DRP library elements by creating downloadable configuration code for the programmable data path hardware and state transition controller (STC)

- Complex algorithms are broken down into smaller "contexts" implemented in the programmable data path hardware

- The STC switches individual contexts into the hardware as processing proceeds, and changes the next required context in a single clock cycle (nanoseconds)

- The result is virtually expandable, configurable data path processing hardware for implementing complex algorithms (time and space-multiplexing)

Extreme Efficiency

- Time and space-multiplexing delivers higher performance and lower power than CPU, GPU or DSP

Using DRP Technology

- Renesas offers a comprehensive and expanding library of image processing functions

DRP Library for RZ/A2M FreeRTOS™ Software Package - Customers can optionally work with approved design partners to develop custom libraries

Dynamic Reconfiguration and Loading to Support Multiple Complex Algorithms

Dynamic Reconfiguration

- The DRP can switch between multiple data paths (contexts) on each DRP clock cycle

- Context switching is managed by the state transition controller, and context loading is operated by the integrated DMAC.

- Time and space-multiplexing can execute complex algorithms with fixed DRP area without hardware area expansion.

Dynamic Loading

- The DRP can accelerate multiple, different algorithms in your application

- Completely new configurations can be loaded into the DRP in as little as 1 millisecond

- Dynamic loading can realize implementation of additional features without hardware revision during operation

DRP Accelerates Embedded Machine Vision

- The DRP speeds image pre-processing and reduces data size for further processing

- The RZ/A2M MPU provides high-speed and low-power machine vision solutions by enabling hybrid image processing with the DRP and CPU