Overview

Description

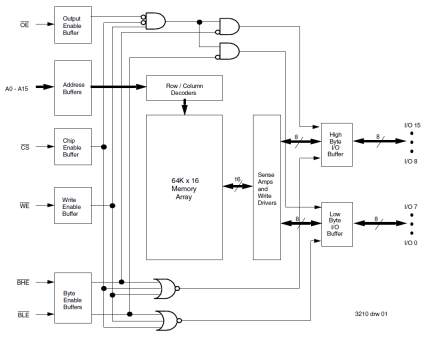

The 71016 5V CMOS SRAM is organized as 64K x 16. All bidirectional inputs and outputs of the 71016 are TTL compatible and operation is from a single 5V supply. Fully static asynchronous circuitry is used, requiring no clocks or refresh for operation.

Features

- Equal access and cycle times – Commercial and Industrial: 12/15/20ns

- One Chip Select plus one Output Enable pin

- Bidirectional data inputs and outputs directly TTL compatible

- Low power consumption via chip deselect

- Upper and Lower Byte Enable Pins

- Available in 44-pin Plastic SOJ and 44-pin TSOP packages

Comparison

Applications

Documentation

Featured Documentation

Log in required to subscribe

|

|

|

|

|---|---|---|

| Type | Title | Date |

| Datasheet | PDF 99 KB | |

| Guide | PDF 182 KB 日本語 | |

| Guide | PDF 1.27 MB 日本語 | |

| End Of Life Notice | PDF 938 KB | |

| End Of Life Notice | PDF 909 KB | |

| Product Change Notice | PDF 155 KB | |

| Product Change Notice | PDF 834 KB | |

| Product Change Notice | PDF 748 KB | |

| Product Change Notice | PDF 108 KB | |

9 items

|

||

Design & Development

Models

ECAD Models

Schematic symbols, PCB footprints, and 3D CAD models from SamacSys can be found by clicking on products in the Product Options table. If a symbol or model isn't available, it can be requested directly from the website.

Product Options

Applied Filters: