概要

説明

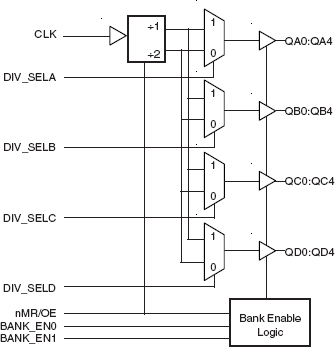

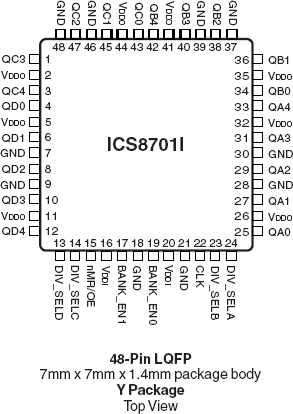

The 8701I is a low skew, ÷1, ÷2 Clock Generator. The low impedance LVCMOS outputs are designed to drive 50Ω series or parallel terminated transmission lines. The effective fanout can be increased from 20 to 40 by utilizing the ability of the outputs to drive two series terminated lines. The divide select inputs, DIV_SELx, control the output frequency of each bank. The outputs can be utilized in the ÷1, ÷2 or a combination of ÷1 and ÷2 modes. The bank enable inputs, BANK_EN0:1, support enabling and disabling each bank of outputs individually. The master reset input, nMR/OE, resets the internal frequency dividers and also controls the active and high impedance states of all outputs. The 8701I is characterized at 3.3V and mixed 3.3V input supply, and 2.5V output supply operating modes. Guaranteed bank, output and part-to-part skew characteristics make the 8701I ideal for those clock distribution applications demanding well defined performance and repeatability.

特長

- Twenty LVCMOS outputs, 7Ω typical output impedance

- LVCMOS / LVTTL clock input

- Maximum input frequency: 250MHz

- Bank enable logic allows unused banks to be disabled in reduced fanout applications

- Bank skew: 200ps

- Output skew: 250ps

- Multiple frequency skew: 300ps

- Part-to-part skew: 600ps

- 3.3V or mixed 3.3V input, 2.5V output operating supply

- -40°C to 85°C ambient operating temperature

- Other divide values available on request

- Available in lead-free RoHS compliant package

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。