概要

説明

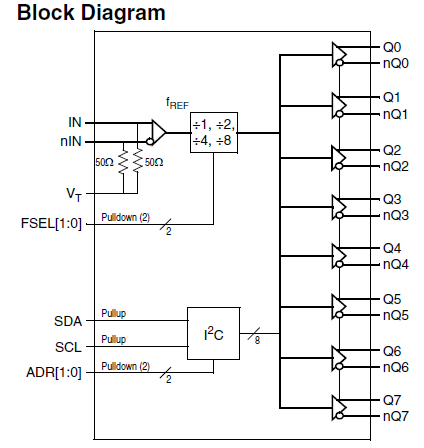

The 8T73S208B-01 is a high-performance differential LVPECL clock divider and fanout buffer. The device is designed for the frequency division and signal fanout of high-frequency, low phase-noise clocks. The 8T73S208B-01 is characterized to operate from a 2.5V and 3.3V power supply. Guaranteed output-to-output and part-to-part skew characteristics make the 8T73S208B-01 ideal for those clock distribution applications demanding well-defined performance and repeatability. The integrated input termination resistors make interfacing to the reference source easy and reduce passive component count. Each output can be individually enabled or disabled in the high-impedance state controlled by a I2C register. On power-up, all outputs are disabled.

特長

- One differential input reference clock

- Differential pair can accept the following differential input levels: LVDS, LVPECL, CML

- Integrated input termination resistors

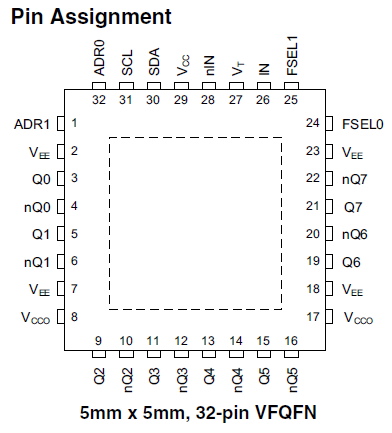

- Eight LVPECL outputs

- Selectable clock frequency division of ÷1, ÷2, ÷4 and ÷8

- Maximum input clock frequency: 1GHz

- LVCMOS interface levels for the control inputs

- Individual output enable/disabled by I2C interface

- Power-up state: all outputs disabled

- Output skew: 60ps (maximum)

- Output rise/fall times: 350ps (maximum)

- Low additive phase jitter, RMS: 182fs (typical)

- Full 2.5V and 3.3V supply voltages

- Lead-free (RoHS 6) 32-Lead VFQFN packaging

- -40°C to 85°C ambient operating temperature

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。