概要

説明

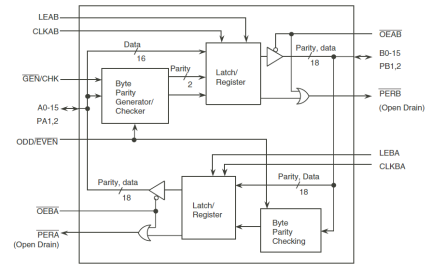

The 74FCT162511T 16-bit high-speed, low-power registered/latched transceiver with parity combines D-type latches and D-type flip-flops to allow data flow in transparent, latched, or clocked modes. The device has a parity generator/ checker in the A-to-B direction and a parity checker in the B-to-A direction. The 74FCT162511T operates at -40C to +85C

特長

- A and C speed

- Typical tsk(o) (Output Skew) 250ps, clocked mode

- Low input and output leakage ?1 uA (max)

- ESD > 2000V per MIL-STD-883, Method 3015

- > 200V using machine model (C = 200pF, R = 0)

- VCC = 5V ±10%

- Balanced Output Drivers: ±24mA

- Series current limiting resistors

- Generate/Check, Check/Check modes

- Open drain parity error allows wire-OR

- Available in 56 pin SSOP and TSSOP packages

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。