概要

説明

Support is limited to customers who have already adopted these products.

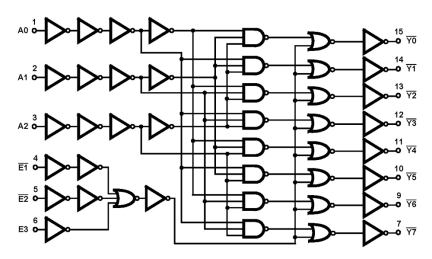

The Intersil HCTS138MS is a Radiation Hardened 3-to-8 line Decoder/Demultiplexer. The outputs are active in the low state. Two active low and one active high enables (E1, E2, E3) are provided. If the device is enabled, the binary inputs (A0, A1, A2) determine which one of the eight normally high outputs will go to a low logic level. The HCTS138MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of radiation hardened, high-speed, CMOS/SOS Logic Family. The HCTS138MS is supplied in a 16 lead Ceramic flatpack (K suffix) or a SBDIP Package (D suffix).

特長

- 3 Micron Radiation Hardened SOS CMOS

- Total Dose 200K RAD (Si)

- SEP Effective LET No Upsets: >100 MEV-cm2/mg

- Single Event Upset (SEU) Immunity < 2 x 10-9 Errors/ Bit-Day (Typ)

- Dose Rate Survivability: >1 x 1012 RAD (Si)/s

- Dose Rate Upset >1010 RAD (Si)/s 20ns Pulse

- Latch-Up Free Under Any Conditions

- Fanout (Over Temperature Range)

- Bus Driver Outputs - 15 LSTTL Loads

- Military Temperature Range: -55°C to +125°C

- Significant Power Reduction Compared to LSTTL ICs

- DC Operating Voltage Range: 4.5V to 5.5V

- LSTTL Input Compatibility

- VIL = 0.8V Max

- VIH = VCC/2 Min

- Input Current Levels Ii ≤ 5µA at VOL, VOH

製品比較

アプリケーション

ドキュメント

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| データシート | PDF 434 KB | |

| カタログ | PDF 5.02 MB | |

| カタログ | PDF 467 KB | |

| Product Advisory | PDF 499 KB | |

| 製品変更通知 | PDF 230 KB | |

| EOL通知 | PDF 48 KB | |

| アプリケーションノート | PDF 338 KB | |

7件

|

||

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。