概要

説明

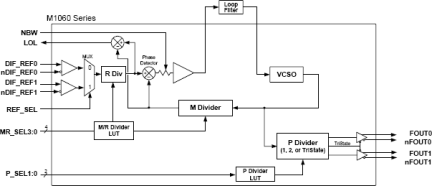

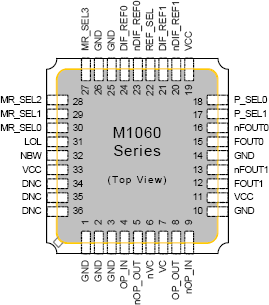

The M106x Series Voltage Controlled SAW Oscillator (VCSO) based clock PLLs are designed for FEC clock ratio translation in 10Gb optical systems such as OC-192 or 10GbE. They support Forward Error Correction (FEC) clock multiplication ratios, both forward (mapping) and inverse (de-mapping). Multiplication ratios are pin-selected from pre-programming look-up tables.

特長

- Integrated SAW delay line

- Output of 62.5MHz to 175MHz

- Low phase jitter < 0.5ps RMS typical (12kHz to 20MHz or 50kHz to 80MHz)

- Pin-selectable PLL divider ratios support FEC ratios

- M1060/65: OTU1 (255/238) and OTU2 (255/237) Mapping

- M1061/66: OTU1 (238/255) or OTU2 (237/255) De-mapping

- M1062/67: OTU1 (238/255) and OTU2 (237/255) De-mapping

- LVPECL clock output

- Reference clock inputs support differential LVDS, LVPECL, as well as single-ended LVCMOS, LVTTL

- Loss of Lock (LOL) output pin

- Narrow bandwidth control input (NBW pin) to adjust loop bandwidth

- Hitless Switching (HS) options with or without Phase Build-out (PBO) are available to enable SONET (GR-253)/SDH (G.813) MTIE and TDEV compliance during reference clock reselection

- Single 3.3V power supply

- Small 9mm x 9mm surface mount package

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。