概要

説明

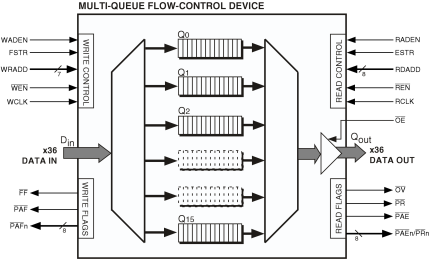

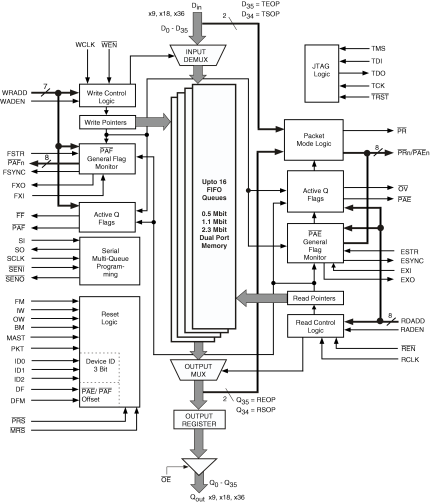

The 72V51456 multi-queue flow-control device is a single chip within which between 1 and 16 discrete FIFO queues can be setup. All queues within the device have common data input bus, (write port) and a common data output bus, (read port). Data written into the write port is directed to a respective queue via an internal de-multiplex operation, addressed by the user. Data read from the read port is accessed from a respective queue via an internal multiplex operation, addressed by the user.

特長

- Total Available Memory = 2,359,296 bits

- Available Memory in blocks of 256 x 36

- Independent Read and Write access per queue

- 100% Bus Utilization, Read and Write on every clock cycle

- 166 MHz High speed operation (6ns cycle time)

- 3.7ns access time

- Global Bus Matching - (All Queues have same Input Bus Width and Output Bus Width)

- User Selectable Bus Matching Options: – x36in to x36out – x18in to x36out – x9in to x36out – x36in to x18out – x36in to x9out

- FWFT mode of operation on read port

- JTAG Functionality (Boundary Scan)

- Available in a 256-pin PBGA package

- Industrial temperature range (-40C to +85C) is available

製品比較

アプリケーション

ドキュメント

ピックアップ

ログイン後、ご登録が可能となります。

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| データシート | PDF 563 KB | |

| EOL通知 | PDF 1.43 MB | |

| 製品変更通知 | PDF 24 KB | |

| 製品変更通知 | PDF 80 KB | |

| 製品変更通知 | PDF 211 KB | |

| 製品変更通知 | PDF 26 KB | |

6件

|

||

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。