概要

説明

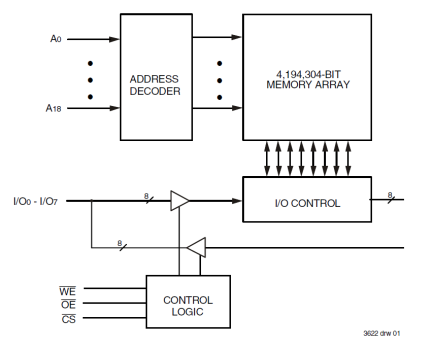

The 71V424 3.3V CMOS SRAM is organized as 512K x 8. All bidirectional inputs and outputs of the 71V424 are TTL-compatible and operation is from a single 3.3V supply. Fully static asynchronous circuitry is used, requiring no clocks or refresh for operation.

特長

- JEDEC Center Power/GND pinout for reduced noise

- Equal access and cycle times

- Commercial and Industrial: 10/12/15ns

- Single 3.3V power supply

- One Chip Select plus one Output Enable pin

- Bidirectional data inputs and outputs directly

- TTL-compatible

- Low power consumption via chip deselect

- Available in 36-pin, 400 mil plastic SOJ and 44-pin, 400 mil TSOP packages

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。