概要

説明

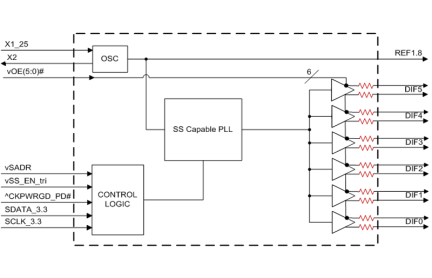

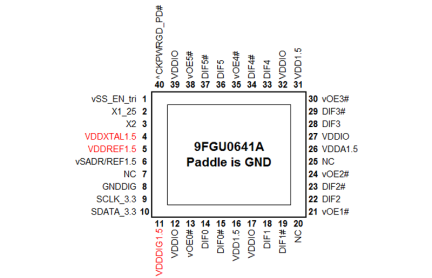

The 9FGU0641 is a member of Renesas' 1.5V ultra-low power PCIe clock family with integrated output terminations providing Zo = 100Ω. The device has six output enables for clock management and supports two different spread spectrum levels in addition to spread off.

For information regarding evaluation boards and material, contact your local sales representative.

特長

- Direct connection to 100ohm transmission lines; saves 24 resistors compared to standard PCIe devices

- 45mW typical power consumption; reduced thermal concerns

- Outputs can optionally be supplied from any voltage between 1.05V and 1.5V; maximum power savings

- OE# pins; support DIF power management

- Programmable slew rate for each output; allows tuning for various line lengths

- Programmable output amplitude; allows tuning for various application environments

- DIF outputs blocked until PLL is locked; clean system start-up

- Selectable 0%, -0.25%, or -0.5% spread on DIF outputs; reduces EMI

- External 25MHz crystal; supports tight ppm with 0ppm synthesis error

- Configuration can be accomplished with strapping pins; SMBus interface is not required for device control

- 3.3V tolerant SMBus interface works with legacy controllers

- Space saving 6mm x 6mm 48-pin VFQFPN; minimal board space

- Selectable SMBus addresses; multiple devices can easily share an SMBus segment

製品比較

アプリケーション

設計・開発

ソフトウェア/ツール

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

ビデオ&トレーニング

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

Watch the Video Series Below