概要

説明

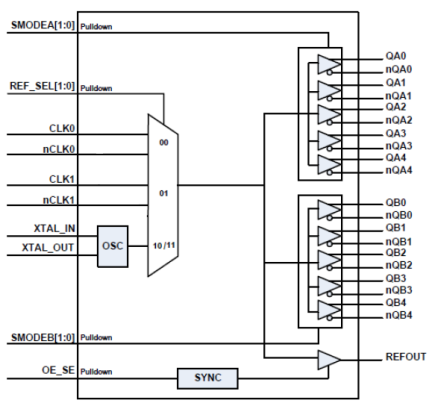

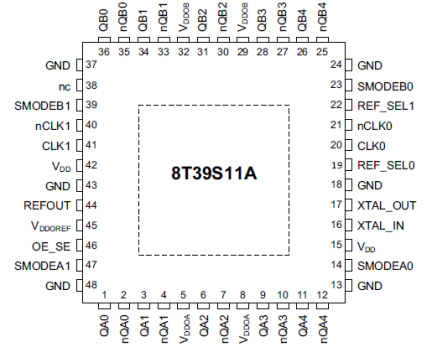

8T39S11Aは、高性能なクロックファンアウトバッファです。 入力クロックは、2つの差動入力または1つの水晶振動子入力から選択することができます。 水晶振動子入力を選択しない場合、内部オシレータ回路は自動的に停止します。 水晶ピンはシングルエンドクロックで駆動できます。選択された信号は、LVPECL、LVDS、またはHSCL出力として構成可能な10個の差動出力に分配されます。 また、LVCMOS出力も備えています。 すべての出力はハイインピーダンス状態に無効にすることができます。 このデバイスは、高周波、低位相ノイズのクロック信号やデータ信号の信号ファンアウトに対応した設計になっています。 入力がオープンまたはグランドの際に、出力は定義されたレベルになります。 3.3Vまたは2.5Vのコア電源と3.3Vまたは2.5Vの出力動作電源で動作するように設計されています。

特長

- Two differential reference clock input pairs

- Differential input pairs can accept the following differential input

levels: LVPECL, LVDS, HCSL, HSTL or Single Ended - Crystal Input accepts 10MHz to 40MHz Crystal or Single Ended Clock

- Maximum Output Frequency

LVPECL - 2GHz

LVDS - 2GHz

HCSL - 250MHz

LVCMOS - 250MHz - Two banks, each has five differential output pairs that can be

configured as LVPECL or LVDS or HCSL - One single-ended reference output with synchronous enable to avoid clock glitch

- Output skew: 80ps (maximum)

(Bank A and Bank B at the same output level) - Part-to-part skew: 200ps (typical)

- Additive RMS phase jitter @ 156.25MHz:

5.6fs RMS (10kHz - 1 MHz), typical @ 3.3V/ 3.3V

34.7fs RMS (12kHz - 20MHz), typical @ 3.3V/ 3.3V - Supply voltage modes:

VDD/VDDO

3.3V/3.3V

3.3V/2.5V

2.5V/2.5V - -40°C to 85°C ambient operating temperature

- Lead-free (RoHS 6) packaging

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

ビデオ&トレーニング

ニュース&ブログ

| Buff Up Your Design with Renesas Clock Buffers | ブログ | 2018年12月15日 |