概要

説明

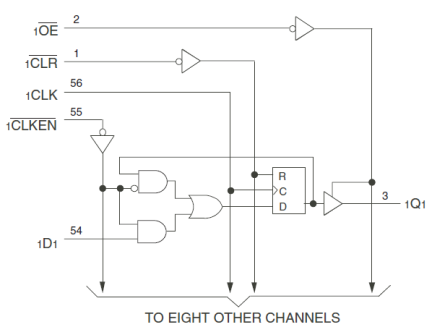

The 74FCT162823T 18-bit high-speed, low-power bus interface register with clock enable (xCLKEN) and clear (xCLR) controls are ideal for parity bus interfacing in high-performance synchronous systems. The device can operate as two 9-bit registers or one 18-bit register. The 74FCT162823T offers low ground bounce, minimal undershoot, and controlled output fall times – reducing the need for external series terminating resistors. The 74FCT162823T operates at -40 °C to +85 °C.

特長

- A and C speeds

- High-speed, low-power CMOS

- Typical tSK(o) (output skew) < 250ps

- Low input and output leakage ≤1µA (max.)

- VCC = 5V ±10%

- Balanced output drivers of ±24mA

- Reduced system switching noise

- Typical VOLP (Output Ground Bounce) < 0.6V at VCC = 5V, TA = 25 °C

- Available in 56-pin SSOP and TSSOP packages

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。