概要

説明

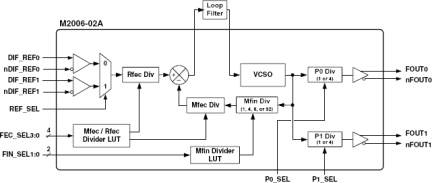

The M2006-02A is a VCSO (Voltage Controlled SAW Oscillator) based clock generator PLL designed for clock frequency translation and jitter attenuation. The device supports both forward and inverse FEC (Forward Error Correction) clock multiplication ratios. Multiplication ratios are pin-selected from pre-programming look-up tables.

特長

- Reduced intrinsic output jitter and improved power supply noise rejection compared to M2006-02

- Low phase jitter of 0.25 ps rms typical (12kHz to 20MHz or 50kHz to 80MHz)

- Pin-selectable PLL divider ratios support forward and inverse FEC ratio translation, including:

- 255/238 (OTU1) Mapping and 238/255 De-mapping

- 255/237 (OTU2) Mapping and 237/255 De-mapping

- 255/236 (OTU3) Mapping and 236/255 De-mapping

- Input reference and VCSO frequencies up to 700MHz, supports loop timing modes (Specify VCSO frequency at time of order)

- Supports active switching between inverse-FEC and non-FEC clock ratios (same VCSO center frequency)

- Ideal for complex ratio FEC ratio translation and for use with an unstable reference (i.e., similar to the M2006-12A - and pin-compatible - but without the Hitless Switching and Phase Build-out functions)

- Single 3.3V power supply

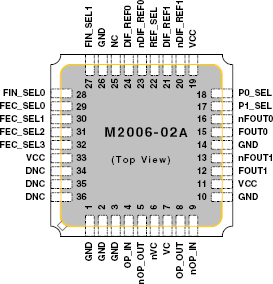

- Small 9 x 9 mm SMT (surface mount) package

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。