概要

説明

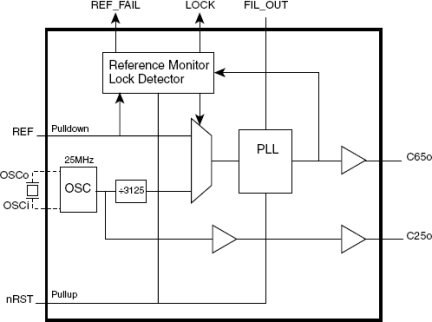

The 8400110I is a Low Jitter Telecom Rate- Conversion PLL that provides accurate and reliable frequency conversion. The 8400110I generates a 65.536MHz clock that is either locked to the input reference or locked to the external crystal or oscillator. In the locked mode, the reference input is continuously monitored for a failure condition. In the event of a failure, the PLL continues to provide a stable free-running clock, ensuring system reliability.

特長

- One 65.536MHz output, synchronized to 8kHz reference

- One 25MHz output, buffered version of the internal osc output

- Provides lock and reference fail indication

- Free run mode when reference clock (REF) fails

- Automatic switch-over to reference when good reference (REF) is available

- 25MHz external master clock source: crystal or oscillator

- Full 3.3V operation

- -40°C to 85°C ambient operating temperature

- Available in a lead-free (RoHS 6) package

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。