概要

説明

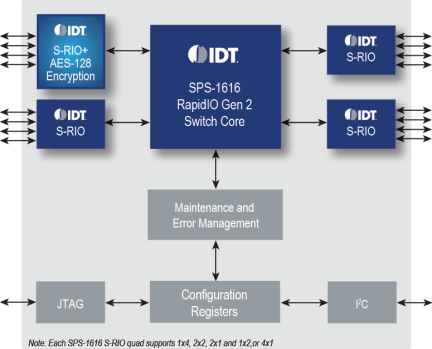

The IDT SPS-1616 Security Enabled Serial RapidIO Gen2 switch is designed for systems that need RapidIO links to go from chassis to chassis with out-of the-box cabling requiring secure/encrypted packets. Using AES-128 encryption the SPS-1616 allows Wireless Infrastructure design engineers to create scalable, stackable systems with up to 20 Gbps between chassis, without having to use expensive encryption cable processors that induce high latency due to software involvement. With the SPS-1616 the security requirements for LTE can be met, while keeping up with line rate between chassis. The SPS-1616 features one quad with Security Capability with the other three quads supporting standard RapidIO only for inside-the-box links.

In addition to the above, the SPS-1616 supports all RapidIO features available in the pin-compatible CPS-1616 including a full, non-blocking bandwidth of 80 Gbps for up to 16x1 ports. The device uses a 5th generation switch fabric, building upon IDT's Gen 1 switching architecture. This new switch uses patent-pending features to minimize latency, ensure scheduling fairness, and provide superior multicast throughput. The additional security feature has zero impact to latency and throughput.

Learn more: IDT RapidIO Development Systems

特長

- Designed to Serial RapidIO 2.1 Specification

- One Security Enabled Quad configurable as 1x4 with security or in RapidIO 2.1 mode as 1x4 or 4x1

- Full duplex 80 Gbps non-blocking bandwidth

- RapidIO Error Management Extension support

- Cut-through latency of 100 ns

- Long reach 100-cm with 2 connectors

- Three Standard quads configurable as 1x4, 2x2, 4x1

- Up to 40% power-per-gigabit savings vs. RapidIO 1.3 switches

製品比較

アプリケーション

設計・開発

ビデオ&トレーニング

Description

Transcript