概要

説明

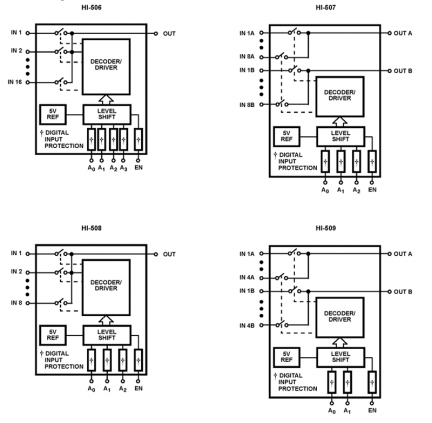

The HI-506/HI-507 and HI-508/HI-509 monolithic CMOS multiplexers each include an array of sixteen and eight analog switches respectively, a digital decoder circuit for channel selection, voltage reference for logic thresholds, and an enable input for device selection when several multiplexers are present. The Dielectric Isolation (DI) process used in fabrication of these devices eliminates the problem of latchup. DI also offers much lower substrate leakage and parasitic capacitance than conventional junction isolated CMOS (see Application Note AN520). The switching threshold for each digital input is established by an internal +5V reference, providing a guaranteed minimum 2. 4V for logic 1 and maximum 0. 8V for logic 0. This allows direct interface without pullup resistors to signals from most logic families: CMOS, TTL, DTL and some PMOS. For protection against transient overvoltage, the digital inputs include a series 200Ω resistor and diode clamp to each supply. The HI-506 is a single 16-channel, the HI-507 is an 8-channel differential, the HI-508 is a single 8-channel and the HI-509 is a 4-channel differential multiplexer. If input overvoltages are present, the HI-546/HI-547/HI-548/ HI-549 multiplexers are recommended.

特長

- Pb-Free Available (RoHS Compliant) (See Ordering Info)

- Low ON Resistance 180Ω

- Wide Analog Signal Range ±15V

- TTL/CMOS Compatible

- Access Time 250ns

- Maximum Power Supply 44V

- Break-Before-Make Switching

- No Latch-Up

- Replaces DG506A/DG506AA and DG507A/DG507AA

- Replaces DG508A/DG508AA and DG509A/DG509AA

- Pb-Free Available (RoHS Compliant)

製品比較

アプリケーション

- Data Acquisition Systems

- Precision Instrumentation

- Demultiplexing

- Selector Switch

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。