概要

説明

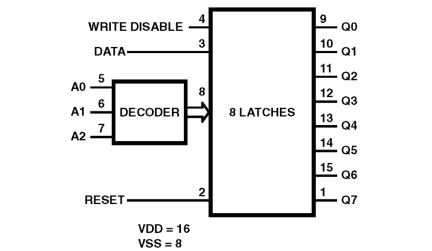

The CD4099BMS 8-bit addressable latch is a serial input, parallel output storage register that can perform a variety of functions. Data are inputted to a particular bit in the latch when that bit is addressed (by means of inputs A0, A1, A2) and when WRITE DISABLE is at a low level. When WRITE DISABLE is high, data entry is inhibited; however, all 8 outputs can be continuously read independent of WRITE DISABLE and address inputs. A master RESET input is available, which resets all bits to a logic 0 level when RESET and WRITE DISABLE are at a high level. When RESET is at a high level, and WRITE DISABLE is at a low level, the latch acts as a 1 of 8 demultiplexer; the bit that is addressed has an active output that follows the data input, while all unaddressed bits are held to a logic 0 level. The CD4099BMS is supplied in these 16-lead outline packages: Braze Seal DIP H4X, Frit Seal DIP H1F, Ceramic Flatpack H6W.

特長

- High-voltage type (20V rating)

- Serial data input

- Active parallel output

- Storage register capability

- Master clear

- Can function as demultiplexer

- 100% tested for quiescent current at 20V

- 5V, 10V and 15V parametric ratings

- Standardized symmetrical output characteristics

- Maximum input current of 1µA at 18V over full package temperature range; 100nA at 18V and +25 °C

- Noise margin (over full package temperature range) 1V at VDD = 5V, 2V at VDD = 10V, 2.5V at VDD = 15V

- Meets All Requirements of JEDEC tentative standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

製品比較

アプリケーション

- Multi-line decoders

- A/D converters

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。