概要

説明

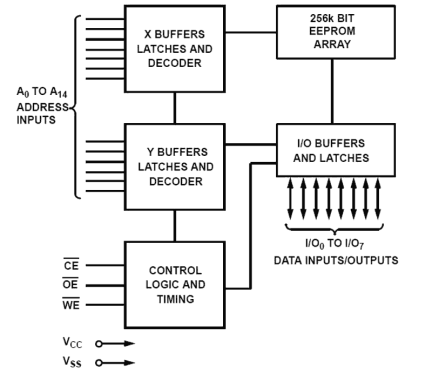

The X28HC256 is a second generation high performance CMOS 32k x 8 EEPROM. It is fabricated with Intersil’s proprietary, textured poly floating gate technology, providing a highly reliable 5V only nonvolatile memory. The X28HC256 supports a 128-byte page write operation, effectively providing a 24μs/byte write cycle, and enabling the entire memory to be typically rewritten in less than 0. 8s. The X28HC256 also features DATA polling and Toggle bit polling, two methods of providing early end of write detection. The X28HC256 also supports the JEDEC standard software data protection feature for protecting against inadvertent writes during power-up and power-down. Endurance for the X28HC256 is specified as a minimum 100, 000 write cycles per byte and an inherent data retention of 100 years

特長

- Access time: 90ns

- Simple byte and page write

- Single 5V supply

- No external high voltages or VP-P control circuits

- Self timed

- No erase before write

- No complex programming algorithms

- No overerase problem

- Low power CMOS

- Active: 60mA

- Standby: 500μA

- Software data protection

- Protects data against system level inadvertent writes

- High-Speed page write capability

- Highly reliable Direct Write™ cell

- Endurance: 100,000 cycles

- Data retention: 100 years

- Early end of write detection

- DATA polling

- Toggle bit polling

- RoHS compliant

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

適用されたフィルター