The VersaClock 3S devices deliver innovative power-saving features while saving board space by eliminating the need for multiple discrete timing components. Delivering low power and low jitter scalability, the VersaClock 3S devices meet requirements for widely used standards including PCI Express® Gen 1/2/3, and are ideal for consumer, industrial, computing, and automotive applications.

The 5P35023 and 5P35021 chips deliver a unique set of features offering an optimal combination of performance, power, and flexibility.

Related Resources

TRANSCRIPT

VersaClock 3S is a family of programmable clocks that deliver innovative features for an optimal blend of performance, power, and flexibility. The compact products can replace multiple crystals, or crystal oscillators, for a smaller board footprint while maintaining extremely low power consumption and are ideal for consumer, industrial, computing, and automotive applications.

VersaClock 3S offers less than three picoseconds of RMS phase jitter and supports PCI Express Generation 1, 2, and 3 requirements. A built-in, digitally controlled oscillator provides a low-frequency clock at less than two microamps per real-time clock operation with several years of operation using a coin-cell battery. Three PLLs optimized for different performance levels offer operation from 2mA to 15mA, and the device features several unique features to balance power and performance. Frequencies up to 160MHz on LVCMOS and up to 500MHz on differential outputs are supported and one-time programmable memory is available for programming.

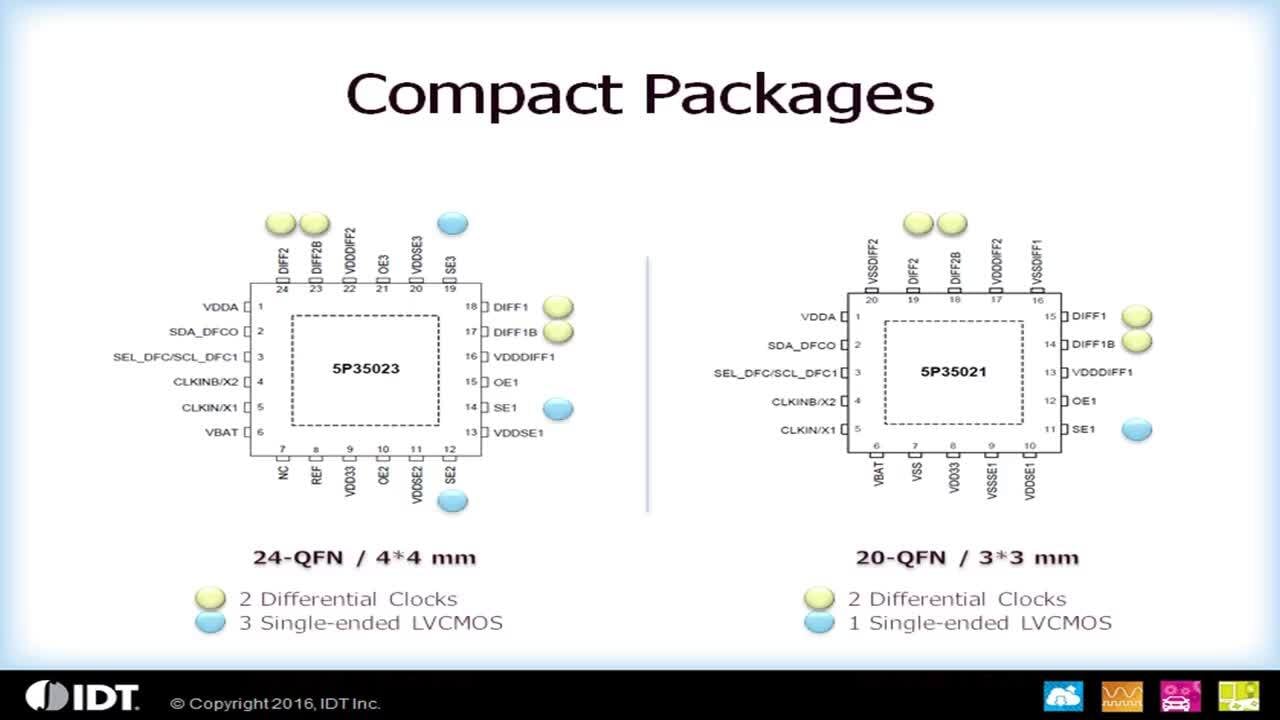

The VersaClock 3S devices are offered in small 3mm x 3mm and 4mm x 4mm QFN packages. The larger device features three LVCMOS and two differential outputs along with a reference clock output. The smaller device offers a single LVCMOS and two differential clock outputs.

VersaClock 3S offers several unique features. A performance power balancing feature supported by the Renesas Timing Commander GUI easily optimizes power consumption based on target performance. A patented overshoot frequency control feature eliminates frequency overshoot or undershoot which is common with traditional PLL designs during frequency transitions. Dynamic frequency control offers smooth and glitch-free transitions between up to four pre-programmed frequencies for on-the-fly frequency changes.

And, VersaClock 3S is the world's first intelligent clock generator with a downstream device power-mode monitor. The proactive power-saving feature monitors the clock status using the Xout pin of the downstream device and will switch to a very low-power 32KHz clock during sleep mode and switch back to normal operation when the downstream device wakes up.

Other device features include a multi-function output that enables pins, along with a built-in watchdog timer. Evaluation and programmer boards along with our Timing Commander software are available to assist with development. The VersaClock 3S family offers an ideal combination of versatility, performance, and low power for a variety of applications. For more information, please visit www.renesas.com/versaclock. Thank you.