ルネサス エレクトロニクス株式会社(代表取締役社長:赤尾 泰、以下ルネサス)はこのたび、次世代システムLSI(28nm(ナノメートル)以降)における標準CMOSロジック回路の設計資産(IP:Intellectual Property)と親和性の高い混載DRAM(embedded DRAM、以下eDRAM)対応の基本構造を開発いたしました。

近年、急速に普及しているデジタルテレビ、デジタルスチルカメラ、ゲーム機器などが扱う画像データは高画質化の一途を辿っており、これらの民生機器や大容量データを処理するサーバならびにネットワーク機器には、より高速かつ低消費電力で実現する技術が強く求められています。そこで当社は、高速処理と低消費電力を両立するデバイスとしてeDRAMを提供しており、その出荷実績は2億個(2010年10月末時点)に達しています。

当社eDRAMの構造は、安定したメモリ動作と十分なデータ保持時間を確保するため、シリコン基板にトランジスタ素子を形成した後、DRAM用の容量素子(キャパシタ)を形成し、その上にこれらを繋ぐ多層配線を形成しています。このため、DRAM用のキャパシタが形成されていないロジック領域においては、トランジスタと配線層間をキャパシタと同じ高さのバイパスコンタクトを介して接続する必要がありました。しかしながら、微細化が進むとバイパスコンタクトの径やその間隔を縮小する必要があります。その結果、バイパスコンタクトの抵抗増大や寄生容量増大の影響を無視できなくなり、従来のように標準CMOSロジックで開発されたIPを、eDRAMに流用することが困難になるという課題がありました。

ルネサスでは、この技術課題を克服する手法の一つとして、絶縁膜材料の工夫などにより、DRAMのキャパシタと配線を同じ層に作りこむ新しい構造を開発し、通常のシステムLSI製造プロセスとの親和性を一段と向上させました。

新技術はロジック回路を構成する配線層内に記憶素子であるキャパシタを埋め込むもので、同技術の採用により、世界的な共通化が進む標準CMOSロジック回路のIPと当社の強みであるeDRAM技術を融合したメモリ混載LSIを実現します。また新技術の採用により、28nm以降の微細プロセスを適用した先端デバイス開発の効率化およびコストの低減が可能になります。

このたび開発した技術の主な特長は以下の通りです。

(1) 従来は配線層と独立した層に設けられていたシリンダ型キャパシタを配線層内に埋め込むことにより、ロジック領域のトランジスタと配線層の間に作りこんでいたバイパスコンタクトを削除。 バイパスコンタクトに起因する寄生容量・寄生抵抗が低減され、ロジック回路の性能劣化を防げるため、28nmノード以降も標準CMOSロジック回路で開発されたIPを活用したeDRAMの設計が可能になる。

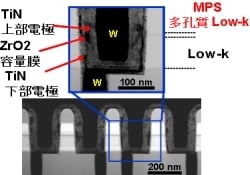

(2) 配線層間膜に独自技術である「独立細孔制御Low-k (Molecular Pore Stack:MPS)膜」を採用することにより、キャパシタの側壁における多孔質Low-k膜内への金属電極材料の拡散を抑制。 これにより、キャパシタ間(50nm厚)の多孔質Low-k膜の絶縁信頼性を10年以上確保できることを確認した。

今回開発した新技術は、キャパシタを配線層内に作りこむことで、バイパスコンタクトを不要とすることから、28nm以降の配線プロセスを適用した先端LSI開発において問題となっていたコンタクトの寄生容量・寄生抵抗を低減し、標準CMOSロジック用に開発されたIPの活用が可能になります。

一方で、配線層内へのキャパシタ形成においては、配線層間絶縁膜中への電極材料侵入による絶縁信頼性の劣化という課題があります。先端LSIでは、高速化と低消費電力化を達成するため、層間絶縁膜として多孔質膜を用いております。キャパシタの電極はこの多孔質膜中に気相成長法で形成されますが、その際に原料ガスが空孔を介して侵入することで性能が劣化するという懸念があります。

この課題に対しては空孔サイズの制御がきわめて重要であり、独自技術である独立細孔制御膜である「MPS膜」を配線層間膜材料として採用することにより、多孔質膜内への金属電極材料の侵入を抑制し、試験で10年以上の絶縁信頼性保証が可能であることを確認いたしました。

このたび開発したeDRAM技術は、グローバルスタンダード化が進む標準CMOSロジックのIPと当社の差異化技術であるeDRAM技術を融合したLSIを、28nm以降の先端製品で実現し、DRAM-ロジック間インタフェースの高速化および低消費電力化を可能にするものです。ルネサスは新技術の早期の実用化を目指して、今後も積極的な研究開発活動を展開してまいります。

なお、当社は今回の成果を、本年12月6日から8日まで米国サンフランシスコで開催される電子デバイス関連の国際学会「IEDM(International Electron Device Meeting) 2010」において、現地時間の8日に発表しました。

以 上

*本リリース中の製品名やサービス名は全てそれぞれの所有者に属する商標または登録商標です。

ニュースリリースに掲載されている情報(製品価格、仕様等を含む)は、発表日現在の情報です。 その後予告なしに変更されることがございますので、あらかじめご承知ください。