ルネサス エレクトロニクス株式会社(代表取締役社長兼CEO:呉 文精、以下ルネサス)はこのたび、IoT(Internet of Things)/ホームエレクトロニクス/ヘルスケア機器用ASSP (Application Specific Standard Product、特定用途向け汎用LSI)に内蔵する、低消費電力SRAMの回路技術を開発しました。新技術の特長は、CPUコアのデータ処理に対応して、内蔵SRAMの読み出し・書き込み動作を行うアクティブ動作と、保持データを失うことなく待機するスタンバイ状態を、少ない電力オーバーヘッドで動的に切り替える機能を有する点です。

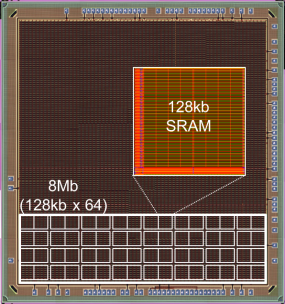

今回ルネサスは、独自に開発を進めてきたSOTB(Silicon-On-Thin-BOX)プロセス技術を採用し、65nm(ナノメートル、ナノは10億分の1)ノードのSOTBプロセスによる内蔵SRAMの試作において、アクティブ動作時の高速読み出し時間を1.8ns(ナノ秒)と、スタンバイ時の超低消費電力 13.7 nW/Mbit(ナノワット/メガビット)の実現を確認しました。これは、SOTB構造の利点を生かした基板バイアス動的制御により、世界最小 (注)の超低電力スタンバイ特性を実現しています。

近年、市場が急成長しているIoT分野では、すべての機器がワイヤレスで接続されることが見込まれており、機器を構成するASSPには、光や振動、熱などの自然エネルギー源を用いた、バッテリレスまたは低電力、電池長寿命化への期待が高まっています。また、電池の長寿命化につながるため、メンテナンスを不要とする電池交換フリーな機器の実現が可能という利点もあります。

一方、IoT機器開発においては、機器の小型化が重要な課題となっており、ASSPの消費電力が少なくとも1桁低減されれば、既存の電池容量を削減し、小型化を実現することができます。

これらIoT向けASSPの低電力化に向けた取り組みとして、通常では待ち受けのスタンバイ状態とし、データ処理が必要な時のみアクティブ状態となって間欠的に動作させる方法があります。具体的にはスタンバイ時の待機電力を下げるため、回路の電源を遮断し必要なデータは一旦外付け、もしくはチップに内蔵する不揮発メモリにデータを退避させる手法が一般的です。しかしこの手法は、待ち受け時間が比較的長い場合は有効的ですが、頻繁にアクティブとスタンバイが繰り返して間欠動作するようなシステムの場合は、不揮発メモリへの退避および再開の動作がオーバーヘッドとなり、逆に消費電力が増えてしまうケースがあります。今回の新技術は、この間欠動作をより頻繁に制御しても電力が増加しないように、内蔵SRAMのスタンバイ時の電力を下げる手法を採用することで、不揮発メモリにデータを退避させる必要がなくなるため、電力効率を高めることが可能となりました。

ルネサスはこれまで、先端プロセス技術を採用した28nm HKMG (High-K Metal Gate) 構造の内蔵SRAMや、16nm FinFET (Fin Field Effect Transistors)構造の高性能内蔵SRAMを試作し、車載情報機器用SoC「R-Car」に搭載しています。そしてこのたび、IoT、ホームエレクトロニクス、ヘルスケア分野に必要とされる低電力性能を実現するため、SOTBプロセス技術を用いて動的に基板バイアスを制御する回路技術を開発、高速動作を実現しつつスタンバイ時の電力を約1/1000に低減することを可能としました。

このたび開発した技術の特長は以下の通りです。

(1)SOTB構造の特長を生かした基板バイアス制御により世界最小の低スタンバイ電力(13.7 nW/Mbit)と高速読み出し動作(1.84ns)を実現

近年、半導体プロセスの微細化と電源電圧の低下に伴い、デバイス素子の低しきい値化によるリーク電流増大と、デバイス素子のばらつき増大による動作下限電圧の悪化が問題視されています。そのため、スタンバイ状態での消費電力の増加や、電圧を下げられないため動作電力が増大し、低電力化が進まないという課題があります。

そこでルネサスは、デバイス素子のばらつきを抑え、オン電流とオフ電流の比率改善に優れていることから、独自に開発を進めているSOTB(Silicon-On-Thin-BOX)プロセス技術を採用し、内蔵SRAMを試作することにいたしました。SOTBプロセス技術は、従来のシリコン基板上に形成したプレーナ型のトランジスタ構造とは異なり、ウエハ基板上の薄いシリコン層の下に埋め込み酸化膜層(BOX: Buried Oxide)が形成されたもので、薄膜シリコン層に不純物注入を不要とするドーパントレスチャネルのトランジスタを構成します。ドーパントレスチャネル構造化により、トランジスタのしきい値特性ばらつきを従来のプレーナ型バルク構造に比べて約1/3に低減することができます。このばらつき低減は、最先端デバイスで採用されているFinFET構造と同等の効果を有し、トランジスタの性能ばらつきを抑えることで、0.5V程度の低電圧での安定した動作を実現することが可能となります。さらに、SOTBプロセス技術では、薄いBOX層を採用し、BOX層下のシリコン基板電位を制御することでトランジスタのしきい値特性を大きく変えることが可能となりました。これは従来のプレーナ型バルク構造やFinFET構造では実現できなかった特性です。この特長を生かし、基板バイアスの印可状態に応じて3つのアクティブ動作モード (通常モード/低電力モード/高速モード)とスタンバイモードを選択できるようにするため、内蔵SRAMは基板バイアスを動的に制御できるオンチップレギュレータ回路を備えます。

これによりルネサスは、高負荷の演算処理が要求される場合は、通常モードから高速モードに切り替え、基板電位をゼロバイアスからフォワードバイアスに設定することで、読み出しアクセスタイムが4.58nsから1.84nsとなり、通常モードと比べ2.5倍高速化できることを確認しました。一方、スタンバイ状態では、基板電位にリバースバイアスを与えることで、アクティブ動作時の電力から3桁削減(1/1000)となる13.7 nW/Mbitを確認することができました。

(2)細粒度ワード線パルスタイミング最適化回路を開発、最大で2割のアクティブ電力削減を実現

演算処理負荷に応じて、基板バイアスや電源電圧を動的に制御する場合、動作モードに応じて高速動作の実現と低消費電力の実現が可能となります。しかし、すべてのバイアス条件で安定した動作を保証する必要があるため、内蔵SRAMの設計マージン確保が課題となります。SOTB構造を採用したことにより、従来のプレーナ型バルク構造に比べて内蔵SRAMの特性ばらつきを低減することができても、同一チップ内の各メモリセル特性のばらつきは完全にゼロにはできません。そのため、もっともばらつきの大きなメモリセルが動作できるように設計マージンを確保する必要があります。IoT機器向けASSPでは、複数のSRAMマクロをチップ内に配置する場合が多く、もっともばらつきの大きなメモリセルがどのマクロに含まれるかという確率により、個々のSRAMマクロ単位で必要となる設計マージンが変わります。これまでは、チップ内の全マクロが確実に動作するワースト条件を保証するように同じワースト条件の設計マージンを各マクロに割り当てていましたが、マージン過剰なマクロも存在します。

そこでルネサスは今回、細粒度(小マクロ単位)でワード線の読み出しパルスタイミングの最適化を可能とするレプリカ回路方式を開発、過剰な設計マージンの除去を図りました。これにより、読み出し動作時のアクティブ電力を最大2割削減することを可能としました。

今回ルネサスが試作したSOTBプロセス用低電力内蔵SRAMは、今後プロセスの微細化が進むにつれて困難になると予想される動作速度の向上と低スタンバイ電力化を実現しており、低電圧での安定した動作を実現します。ルネサスは、今回試作した内蔵SRAMを搭載した低電力/ASSPがIoT分野における環境発電(Energy Harvest)動作に対応し、電池交換を不要とするメンテナンスフリーの機器開発に寄与できると期待しています。また、この内蔵SRAMを65nm SOTBプロセスを用いたルネサスの低電力ASSPに搭載し、いち早く市場に投入することで、人と環境に優しいスマート社会の実現に貢献します。

なお、当社は今回の成果を、2017年6月5日から京都で開催される「VLSIシンポジウム国際会議(VLSI Symposia 2017)」にて、日本時間の6月8日に発表しました。

以 上

(注)2017年6月8日時点。ルネサス調べ。

*本リリース中の製品名やサービス名は全てそれぞれの所有者に属する商標または登録商標です。

ニュースリリースに掲載されている情報(製品価格、仕様等を含む)は、発表日現在の情報です。 その後予告なしに変更されることがございますので、あらかじめご承知ください。