今日、市場の最も重要な課題の1つは、さまざまな機能を1つのチップに組み合わせてデバイスのサイズを最小限に抑えながら、信号処理とデータ管理に高い柔軟性、効率、および最高の品質を提供することです。 ルネサスのAnalogPAK™ SLG47011は、これらの課題に対処するための優れたソリューションです。

まずは基本から始めましょう - AnalogPAKは、さまざまなシナリオを実装するために、お客様が定義したロジック機能によって設定および制御できる高性能アナログブロックが組み込まれた、幅広いGreenPAK™プログラマブルミックスドシグナル製品ファミリの比較的新しいサブファミリーです。 すべてのマクロセルが1つのICに詰め込まれているため、一般的なアナログおよびデジタル部品の高レベルの統合が実現されています。 このSLG47011は、GreenPAK技術の進化における重要なマイルストーンであり、プログラマブル・ミックスドシグナルICの新時代を切り開くものです。 この最新のチップは、GreenPAKの基本原理に基づいて構築されつつ、その機能を劇的に拡張する高度な機能を導入し、ミックスドシグナル設計における柔軟性、パフォーマンス、統合の新たな基準を打ち立てます。

SLG47011を使用すると、これまで以上に複雑な設計の性能が可能になります。 エンジニアは、プログラマブルゲインアンプ(PGA)、アナログ-デジタルコンバータ(ADC)、デジタル-アナログコンバータ(DAC)、A-DおよびD-A変換の設定、フィルタリング、データストレージ、ゲインおよびオフセット補償など、SLG47011の新しいブロックを使用してMCUの性能をオフロードまたは拡張できます。 アナログ・ブロックとGreenPAKの構成可能なロジックにより、複雑なAFEをMCUに簡単に置き換えることができます。 より優れた省エネのために、すべてのマクロセルに対して柔軟なユーザー定義の省電力モードがあります。 スリープモードでは、チップの消費電流はわずか~0.6μAです。 GreenPAKファミリーは、ミックスド・シグナル・プロジェクト向けに小型パッケージ製品を低コストで提供します。

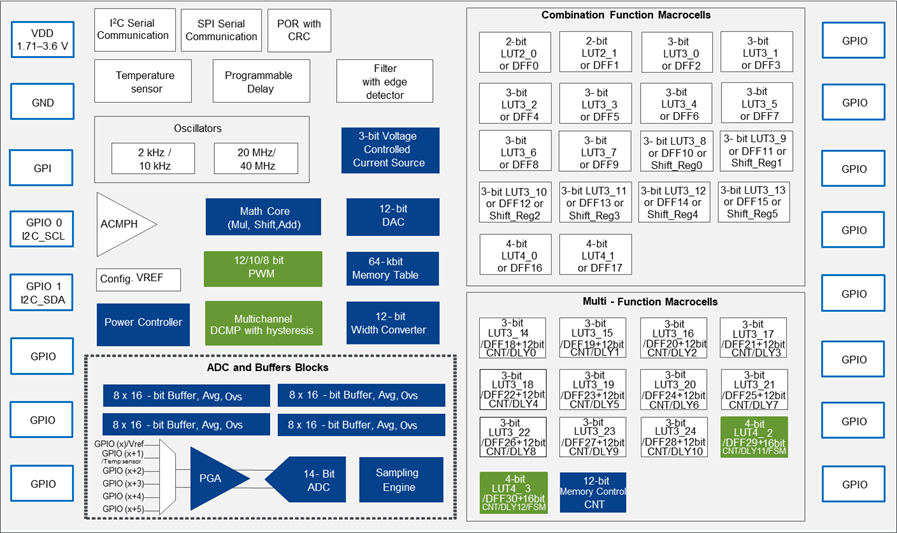

以下に、SLG47011の内部構造を示すブロック図を示します。

上の図からわかるように、LUT、フリップフロップ、シフトレジスタ、タイマー、カウンタ、遅延などの通常のGreenPAKに内蔵されている設定可能なブロックに加えて、SLG47011にはいくつかの新しいブロック(青)と改善されたブロック(緑)もあります。

これらすべてのブロックにより、 SLG47011 はHARTモデム、センサインターフェース(冷接点補償付き熱電対インターフェース、ゲインおよびオフセット誤差補償付きブリッジセンサーインターフェース、センサー用電源としての電流源、内部温度、Vref(Vcc)センシング)、電流/電圧/電力/温度モニターおよび保護、容量性センサーボタン、 RGB LED制御、MPPTコントローラー、といった幅広いアプリケーションをサポートします。

これを可能にするチップ構造を、チップの心臓部であるPGA、ADC、バッファブロックから見てみましょう。 高度に設定可能な低オフセット PGA により、ユーザーは入力信号要件により適したさまざまなアンプ・モードと構成を設定できます。

次に重要なのは、最先端の14ビット逐次比較レジスタA/Dコンバータ(SAR ADC)マクロセルで、14ビットモードで最大1Msps、8ビットモードで2.35Mspsの超高速サンプリングレートを実現します。 パラレルデータ出力、自動キャリブレーション、選択可能なクロックソースなどの機能により、信号処理のニーズに対応する比類のない精度と汎用性を提供します。

当社のチップに搭載された4つの汎用性の高いデータバッファによって、ADCまたはCNT/DLYからのデータを保存または処理できるようにカスタマイズできます。 選択可能な長さと初期データ設定により、ユーザーはストレージ、移動平均、オーバーサンプリングのいずれモードでも、比類のない操作体験をシームレスに調整できます。

さて、SLG47011のメモリの話に移りましょう。 メモリテーブルマクロセル は、12ビットのアドレスとデータポートを持つ4096個の12ビットワードを格納するメモリブロックです。 お客様は、ADCデータバッファリングとI²C/SPIを介した外部転送用のRAMモードと、事前にプログラムされたデータアレイへの迅速なアクセス用のROMモードのいずれかを選択でき、効率的な機能実装と計算遅延のない迅速な線形化を可能にします。

SLG47011には、メモリ テーブル マクロセルから接続マトリックスにデータを提供するように設計された 12 ビット 幅コンバーター マクロセルが 1 つあります。 12ビット・パラレル出力、3つの4ビット・ワード、6つの2ビット・ワード、またはシリアル・ビット・ストリームなど、お好みの出力形式を選択でき、アプリケーション・ニーズに合わせた比類のない柔軟性を提供します。

現在、私たちは大量のデータを受け取り、増幅し、サンプリングし、保存しています。 もうすでに良い製品であることが伝わったと思います。しかし、SLG47011にはもう1つの重要な要素があります - MathCore ブロックです。 この Mathematical Core ブロックは、加算、減算、乗算、除算 (右シフト)、およびそれらの組み合わせの 4 つの数学演算をサポートしています。 MathCoreの入力ソースは、ADCチャンネル、メモリテーブル出力、データバッファ出力、またはレジスタからの定数です。

SLG47011はそれだけにとどまらず、 改良されたヒステリシス付きマルチチャネルデジタルコンパレータマクロセル(DCMP)を追加しています。 最大4つのデジタルチャンネルを同期または順次、結果を比較します。 また、連続サンプリングまたは1回限りの順次サンプリングを選択することも可能です。

上記のブロックに加えて、PWMブロック、12ビットDAC、パワーコントローラ、および多数のロジックセット(LUT、フリップフロップ、カウンタ、遅延など)もあります。

さまざまなソリューションに対応する究極のICであるSLG47011で、信号処理およびデータ管理アプリケーションをレベルアップできます。 複数の機能を1つのチップに統合することで、設計の合理化、基板サイズの縮小、消費電力の削減、部品コストの削減を実現します。 効率的で革新的なSLG47011を使用することで、プロジェクトのパフォーマンスと費用対効果を大きく向上させることができます。

詳細については、 renesas.com/slg47011 にアクセスするか、 キットを注文 して評価を開始してください。