高性能なAIデータセンタは、これまでのどの技術よりも半導体の設計や投資の方向性を大きく変えつつあります。2022年のAIインフラへの投資額はおよそ150億ドルでしたが、今年は600億ドルをゆうに超える勢いとなっています。まさしく、あらゆる投資計画の資金がデータセンタに注ぎ込まれている状況です。

中国のDeepSeekのような新興企業が及ぼしうる影響はあるにせよ、現在AI分野への資本支出が前例のない規模で行われているのは明らかです。NVIDIAやAMDなどのハイパフォーマンスコンピューティング(HPC)向けプロセッサが注目を集めている一方で、学習モデルや推論モデルを格納する高帯域幅メモリ(HBM:High Bandwidth Memory)も脚光を浴びつつあり、2024年のDRAM市場の売上高は過去最高の約1,160億ドルに達する見込みです。

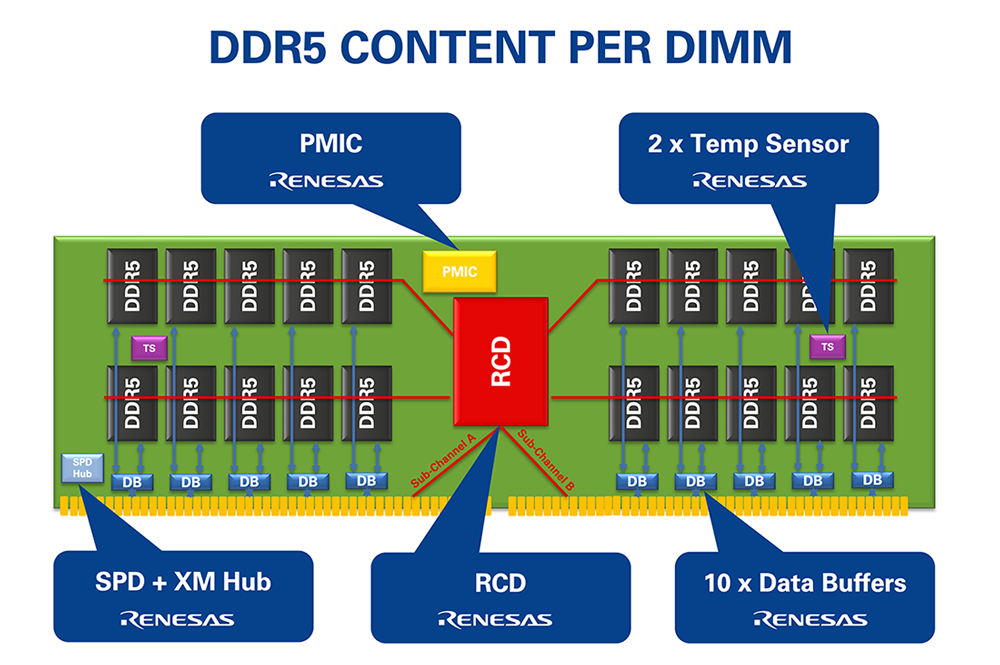

データセンタ用サーバではCPUコア数が増え続けており、各プロセッサコアにより高い帯域幅のデータを供給するには、メモリ容量もさらに拡大する必要があります。 しかし、物理法則上の限界もあります。すなわち、CPUの信号の速度や伝送距離には限界があるのです。そこで登場するのが、レジスタクロックドライバ(RCD)やデータバッファといったメモリインタフェース製品です。これらのデバイスは、クロック、コマンド、アドレス、データといった信号を高い信号品質で再駆動することにより、メモリサブシステム全体の速度と容量の拡張を可能にします。

現在、ルネサスのRCDによってレジスタードDIMM(RDIMM)は8GT/s(ギガトランスファ/秒)で動作可能となっています。多くのデータセンタサーバではRDIMMが使用されていますが、一部のHPCシステムではメモリサブシステムに一層高い性能が求められます。

メモリインタフェースがDRAMとプロセッサの性能をさらに強化

DRAMは、データセンタサーバシステムにおいて重要な役割を担っているものの、そのアーキテクチャ自体は過去30年間でそれほど劇的には変化していません。DRAMの密度や速度、消費電力効率の向上は、その大部分が半導体プロセスの微細化によるものであり、新たな2.5次元および3次元の積層DRAMパッケージング技術によって、より大容量のDIMMモジュールが実現しています。

前述のとおり、メモリインタフェース技術の進歩は、シンクロナスDRAMに始まり複数世代にわたるダブルデータレート(DDR)DRAMへと受け継がれてきており、メモリインタフェースがプロセッサの高速化に対応する上で極めて大きな役割を果たしてきました。

マルチプレックスランクDIMM(MRDIMM)は、AIおよびHPCのデータセンタ用途向けに設計された革新的な技術です。ルネサス、インテル、そしてメモリサプライヤ各社との協業によって実現したMRDIMMにより、対応するサーバシステムのメモリサブシステムはRDIMMと比べてはるかに高い帯域幅へと拡張できます。具体的には、MRDIMMでは2つのランクのメモリが同時にデータを取得できるためホストインタフェースのデータ転送速度が2倍となり、その結果メモリ帯域幅が約6%〜33%拡大します。

ルネサスのDRAMインタフェースがプロセッサとメモリ間の性能ギャップ解消に貢献

ルネサスのDRAMインタフェースがプロセッサとメモリ間の性能ギャップ解消に貢献 2024年11月、ルネサスは第2世代DDR5 MRDIMM向けに、業界初のトータルなメモリインタフェースチップセットソリューションを発表しました。このソリューションは12.8GT/sで動作し、標準的なDIMMの最大データ転送速度8.0GT/sと比べてインタフェース駆動速度が飛躍的に向上しました。

どのようにしてこれを実現できたのでしょうか。それは、複数のコンポーネントを高度に組み合わせた結果です。ルネサスが買収したIntegrated Device Technology(IDT)社は創業当初から、メモリ性能を阻害する重大な問題、すなわちシグナルインテグリティに関する課題の解決という使命に取り組んできました。

DRAMとCPUの速度差が拡大し始めると、DRAMの物理的な負荷がシステム設計者にとって問題となってきました。そこで、アナログおよび混合信号設計の専門技術を活かせばこの課題に対処できると考えました。まず取り組んだのは、DRAMとプロセッサの間でクロック信号とコマンド・アドレス信号を途中で受け取り、再び駆動するRCDの開発です。その後、クロック、コマンド、アドレス、データといったシステムメモリインタフェース上のあらゆる信号を中継するフルバッファDIMMシリーズを開発しました。

そして現在、当社の最新のDDR5メモリインタフェース製品としても、すでにMRDIMM向け第2世代RCDおよびデータバッファに加えてパワーマネジメントIC(PMIC)も提供しています。これにより、ルネサスは次世代のRDIMMおよびMRDIMM向けに完全なチップセットソリューションを提供できる唯一の企業となりました。さらに、ルネサスは「DIMM上での電圧レギュレーション」というコンセプトを推進することで、電力効率の向上にも大きく貢献してきました。このコンセプトにより、電圧レギュレーション用の回路が従来のマザーボード上ではなく直接DIMM上に配置され、より効率的で分散型の電源モデルが可能となっています。これは、DIMM上の各コンポーネントに必要なすべての電圧をローカルに生成、調整するPMICを使用することで実現しています。

将来に向けた電子設計エコシステムの活用

ルネサスは、主要なCPUやメモリのサプライヤ、ハイパースケールデータセンタのユーザ、JEDECをはじめとする標準化団体から成る大規模な設計エコシステムとの協業を通じて、社内に膨大な専門知識を蓄積してきました。この協業体制により、DIMMに何個のDRAMコンポーネントを搭載できるか、またそれらをどの程度の速度で動作させられるかを見極めることで、DIMMの速度と容量を一層向上させる上でのボトルネックを取り除くことが可能になっています。

また、AIデータセンタ向けに開発された技術を活用し、それを新たなユースケースに転用する機会も広がります。これは、産業用ネットワーク制御のエッジにおいてデータを収集し有用な知見へと変換するために要求される、より高い処理性能やメモリ帯域幅にも当てはまります。そして、自動車の安全性や自動運転アプリケーションで必要とされる膨大なデータ量についても同様で、こうした要件によって自動車は急速に「車輪のついたサーバ」となりつつあります。

AI時代の要求に当社のメモリインタフェース技術を適合させるために取り組む中で、ひとつ明らかになったことがあります。それは、データを静止させてはならないということです。データは常に動き続けているのです。そうした中、ルネサスも同様、常に前進し続けています。