FemtoClock™ 3ワイヤレス(3W)には2つの主要なアプリケーションがあります: 1つは224G PAM SerDesリファレンス・クロック用の有線用途、もう1つは「5Gアドバンスト」無線ユニットまたはスモール・セル用の無線用途です。

最近のGPUファーム/ノードAIの急成長により、生成AI向けのすべてのネットワーク速度は112G PAM4から224G PAM4 SerDes(800Gから1.6T)に移行しています。 複数のイーサネット・スイッチ・ベンダーBroadcom、Nvidia、Marvell、Ciscoが、まもなくイーサネットスイッチチップセットソリューションを市場に投入する予定であり、それには超低ジッター・クロック・ソリューションが不可欠です。 FemtoClock 3W(RC38312A)は、このアプリケーションを対象としています。

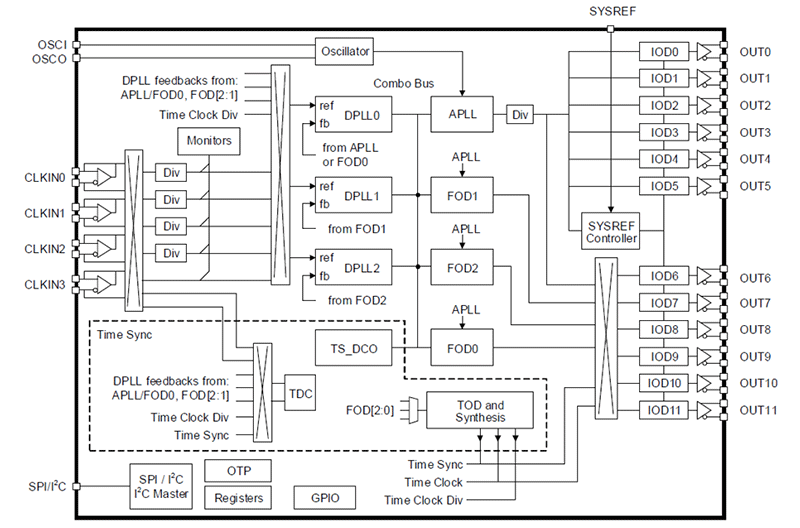

RC38312A機能

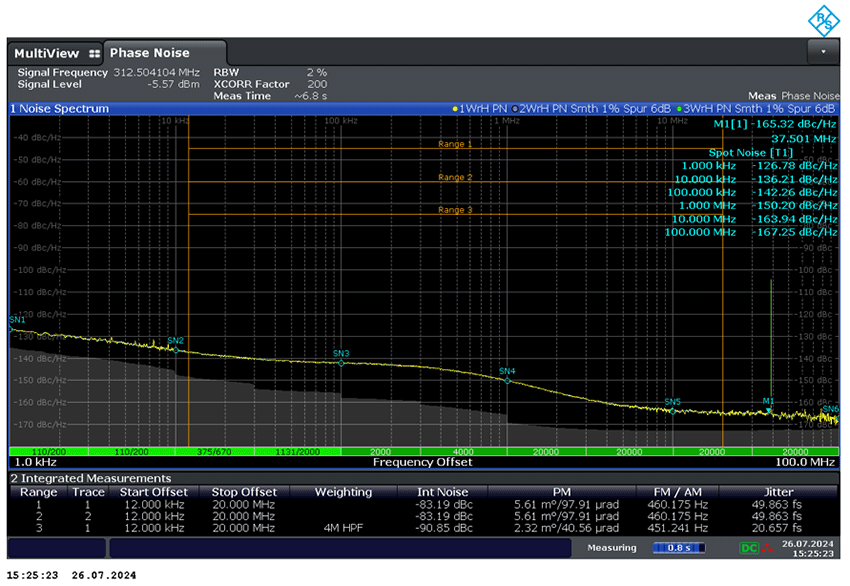

- 4MHzのHPFの条件下で、12kHz-20MHzでのRMSジッタが25fs以下の超低位相ノイズシンセサイザ

- 3つのDPLLと3つのFODにより、4つの周波数ドメインをサポート

- JESD204B/Cのサポート

- 独立した整数分周器を備えた12のクロック出力:

- 8:LVDS、HCSL(AC-LVPECL)またはCML

- 4:LVDS、HCSL(AC-LVPECL)またはLVCMOS

- 出力周波数範囲:

- CML:DCから2.5GHz

- LVDSまたはHCSL:DCから1GHz

- LVCMOS:DCから250MHz

- 4つの差動または8つのシングルエンド・クロック入力

- 1.8Vの単一電源で動作可能

- 消費電力は1.5W未満です

224G PAM4 SerDes のクロック要件

224G PAM4 SerDesのクロック要件は厳しいですが、FemtoClock 3Wはそれらを満たすことができます。 224G PAM4のジッター要件は、4MHzのHPFの条件下で、25fs(12kHz〜20MHz)未満であり、FemtoClock 3Wはこの要件を余裕をもって満たしています。

有線タイミングと無線タイミングの両方をサポート

RFシンセサイザは、最新の高度な通信ソフトウェア無線システムに不可欠なコンポーネントです。 これらのシンセサイザのスペクトル純度は、達成可能な最大データレートとノイズパワー特性に直接影響するため、非常に重要です。 RFアプリケーションでは、シンセサイザは広いチューニング範囲と正確な周波数分解能で高周波を供給する必要があります。 これらの厳しい性能基準を達成するためには、消費電力を抑え、チップ面積を小さくするだけではなく、スプリアスと位相ノイズを最小限に抑える必要があります。

実際の1024-QAMアプリケーションでは、(アイ)ダイアグラムへのジッターの影響を理解することができます このプロトコルは、エラーを減らすのに役立ちます。 商用SDR通信システムでは、最高のクロックジッター性能を実現することが、一流顧客のビジネスを勝ち取るための重要な戦略です。 これは、伝送距離とデータレートに影響します。

高度なアーキテクチャ

4G無線設計では、PLLシステムは外部VCXOを使用して低ジッタークロックソリューションを提供し、JESD204B/CはPLLとFPGAによって設計されていました。 複雑さとコストはイノベーションを引き起こすための重要な問題であり、同期化には別のDPLLが使用されていました。 これにより、タイミングシステムは同期用DPLL、FPGA、および外部VCXOを備えたデュアルループジッターアッテネーターの合計4つのコンポーネントで構成されていました

最新の無線設計に合わせて、FemtoClock 3Wには、低位相ノイズPLL、3つのDPLL、3つの分数分周器(FOD)、コンボバス、SYSREF/JESD204B/Cエンジン、同期アプリケーション用のTimeSyncモジュールを1チップでサポートするといった改良が施されています。

無線アプリケーション向けの超低位相ノイズ

前述のように、位相ノイズはミリ波での無線通信向けのアプリケーションにとって重要です。 FemtoClock 3Wは、BGAパッケージ(低クロストーク)、低位相ノイズPLL(Kronos PLL)、2.5GHzまでのCML出力(高周波出力チャネル)、位相調整、および補償に基づいて設計されています。

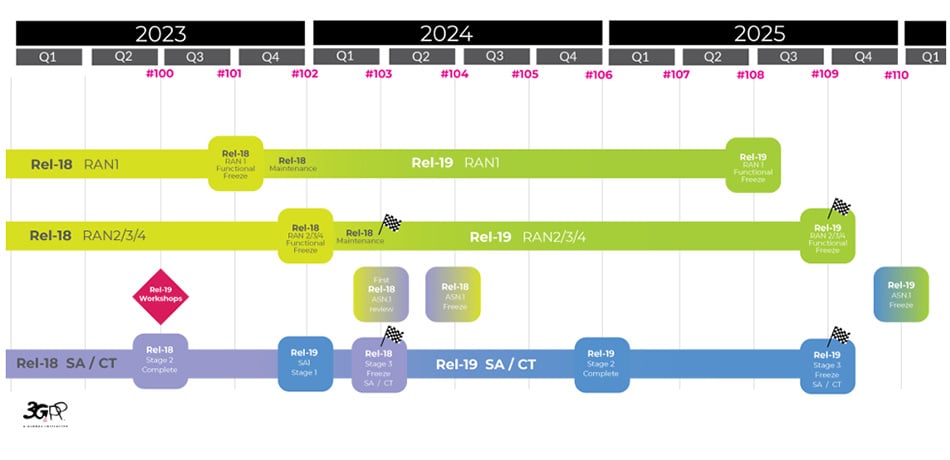

3GPPタイムライン

Rel-19 のコンテンツは 2023 年 12 月の TSG (#102) で決定されましたが、「5G-Advanced」を定義するお客様にとっては非常に重要です。

出典: https://www.3gpp.org/specifications-technologies/releases/release-19

結論

FemtoClock 3Wは、ルネサスの最新のPLL技術で、無線と有線の両方のアプリケーションをサポートします。 1.8Vの単一電源により、消費電力が最も低く、位相ジッタが極めて低いクロック出力を実現します。

FemtoClock 3Wは、無線通信ユニットと1.6Tイーサネットスイッチ用の224G PAM4 SerDesリファレンスクロックの両方に最適なクロックソリューションです。

FemtoClock 3Wの評価を開始するには、今すぐ評価キットを入手してください。