Fixed Form Factor Switch

Pizza-box switches are becoming more common in offices and businesses, and manufacturers have made efforts to add more functionality while reducing costs. Pizza-box styled switches follow a compact design suited for high density, high reliability and flexible deployment. Compared with large rack configuration switches, the power consumption of pizza-box switch equipment can be greatly reduced, as well as the requirements for space, power supply, air conditioning, and other computer room infrastructure, helping operators reduce Total Cost of Ownership (TCO).

Clock Requirements for High-Speed SerDes

In the past decade, with the rapid increase of data rate and the number of data centers, it is now possible to support emerging data-intensive computing applications (such as machine learning and neural networks). If we use the SerDes data rate as an indicator, today's most advanced Pulse Amplitude Modulation 4-Level (PAM4) SerDes runs at 112Gbps. 100G Ethernet can now be supported in a single lane, which was only possible with 180 parallel lanes at the beginning of the 21st century. To support 112Gbps PAM4 technology used to design 400G or 800G Ethernet and optical networks, physical layer reference clocks for the SerDes need to have phase jitter below 150fs RMS. If noise considerations on PCB, restrictions on component layout, signal wiring requirements and power decoupling are added, hardware developers prefer that these physical layer clocks phase jitter closer to 100fs RMS. Since a typical network switch also includes other clocking, including those used for synchronization (more on this in the next section), processors, ASICs, memory, etc., an ultra-high performance timing IC that generates all of the clocking requirements in a single chip is preferred. This helps the PCB designers have a clock tree solution that is optimized for cost, area, power, and performance. Renesas now offers ClockMatrix 2 which addresses all of the aforementioned requirements.

What is Clock Synchronization?

5G is enabling the next frontier of connectivity, aptly named the "Internet of Things", offering the fastest mobile data transfer to date and wide coverage area. This ability to handle new services also poses new challenges to network coverage, network performance and scheduling management. Operators need a wireless network that can handle high data rate and bandwidth, large sets of users, a better business experience, and more efficient operation and maintenance.

In order to achieve network efficiency and guaranteed cell coverage, synchronization is a fundamental prerequisite for all telecommunication networks. 5G networks especially present new challenges, with an increased need for accuracy and reliability in distributing synchronization references throughout the network.

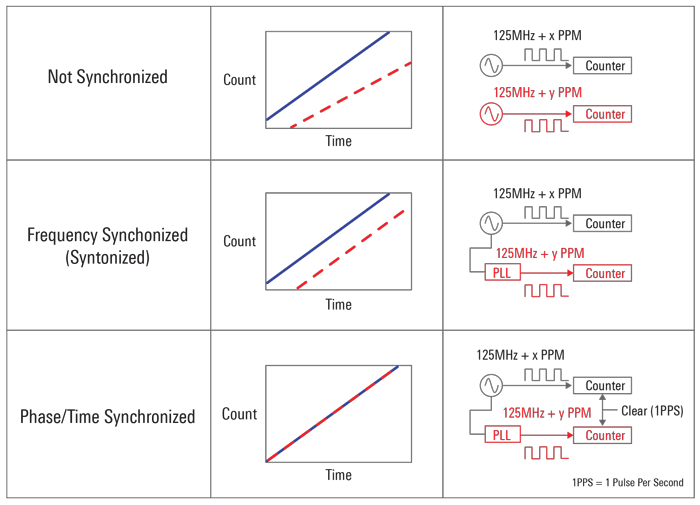

Figure 1 is an example of what would happen in a network that is not synchronized. None of the critical services like mobile handoff (that supports seamless transition of a mobile user’s call or data transfer, while in transit, from one base station to another that prevents dropped calls or aborted data transfer) is possible without having full time and frequency synchronization. In addition, frequency synchronization is needed for optimizing the base station utilization and improving its efficiency. Time synchronization is also needed for time-critical applications and diagnostics.

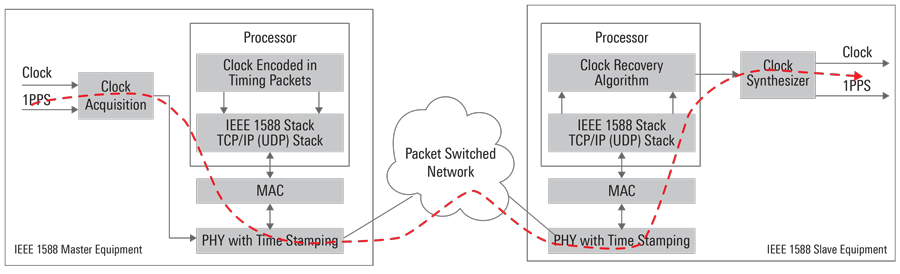

The timing requirements placed on Ethernet systems are becoming increasingly stringent. Traditionally, these systems have been implemented in a centralized architecture in which the timing constraints are met by careful attention to programming combined with communication technologies with deterministic latency. In recent years, an increasing number of such systems utilize a more distributed architecture and modern networking technologies having less stringent timing specifications than the older more specialized technologies. This has led to alternate means for enforcing the timing requirements in such systems. One such technique is the use of system components that contain real-time clocks, all of which are synchronized to each other within the system. The IEEE 1588 Precision Time Protocol (PTP) is a time protocol to transport synchronization across Packet Switched Networks (PSNs). The Master encodes the clock in packets that are transmitted to the Slave. IEEE 1588 can be used in an end-to-end solution without support from the network or it can be used with support from the network (Figure 2).

Introducing ClockMatrix 2

The ClockMatrix 2 is an ultra-high performance, high-precision, multi-channel timing solution that is optimized for 400/800Gbps optical transport and wireline network applications. Building on the ClockMatrix devices introduced in 2019 for 5G wireless and 100/200Gbps wireline network applications, the second-generation family delivers improved performance with phase jitter as low as 88fs RMS.

The highly integrated devices provide all the functionality needed to implement all operating modes of IEEE 1588 with jitter attenuation capabilities. The device provides ultra-low jitter clock outputs that can be used for the synchronous Ethernet SerDes with data rates up to 112Gbps PAM4, reducing design complexity and Bill of Materials (BOM) requirements, while also allowing customers to apply the timing devices to a wide variety of network applications.

Key Features of the ClockMatrix 2 Family

- Highly integrated, 6-channel precision timing source that eliminates the need for additional jitter attenuators for high-speed interfaces

- 88fs RMS phase jitter on clock outputs to support ultra-low jitter clock outputs for high-speed serial links (up to 112Gbps PAM4 SerDes)

- Supports multiple standards and protocols including synchronous Ethernet (Sync-E) and IEEE 1588

- Full compliance to ITU-T G.8262.1 and G.8262 synchronous Ethernet standards and telecom boundary clock requirements as per ITU-T G.8273.2 that exceeds Class C and Class D time accuracy requirements

The ClockMatrix 2 system synchronizer can be combined with Renesas’ complementary analog and power offerings to create comprehensive solutions for a variety of applications. For example, ClockMatrix 2 is integrated into the 200/400/800Gbps Fixed Form Factor Switch Solution winning combination, along with analog and power offerings from Renesas. Renesas offers more than 250 winning combinations with compatible devices for a wide range of applications and end products. They can be found at renesas.com/win.