概要

説明

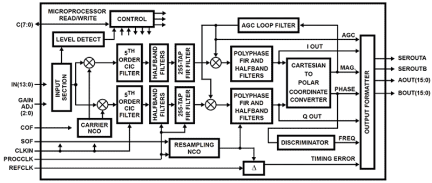

The HSP50214B Programmable Downconverter converts digitized IF data into filtered baseband data which can be processed by a standard DSP microprocessor. The Programmable Downconverter (PDC) performs down conversion, decimation, narrowband low pass filtering, gain scaling, resampling, and Cartesian to Polar coordinate conversion. The 14-bit sampled IF input is down converted to baseband by digital mixers and a quadrature NCO, as shown in the Block Diagram. A decimating (4 to 32) fifth order Cascaded Integrator-Comb (CIC) filter can be applied to the data before it is processed by up to 5 decimate-by-2 halfband filters. The halfband filters are followed by a 255-tap programmable FIR filter. The output data from the programmable FIR filter is scaled by a digital AGC before being re-sampled in a polyphase FIR filter. The output section can provide seven types of data: Cartesian (I, Q), polar (R, θ), filtered frequency (dθ/dt), Timing Error (TE), and AGC level in either parallel or serial format.

特長

- Up to 65MSPS Front-End Processing Rates (CLKIN) and 55MHz Back-End Processing Rates (PROCCLK) Clocks May Be Asynchronous

- Processing Capable of >100dB SFDR

- Up to 255-Tap Programmable FIR

- Overall Decimation Factor Ranging from 4 to 16384

- Output Samples Rates to ≈ 12.94MSPS with Output Bandwidths to ≈ 982kHz Lowpass

- 32-Bit Programmable NCO for Channel Selection and Carrier Tracking

- Digital Resampling Filter for Symbol Tracking Loops and Incommensurate Sample-to-Output Clock Ratios

- Digital AGC with Programmable Limits and Slew Rate to Optimize Output Signal Resolution; Fixed or Auto Gain Adjust

- Serial, Parallel, and FIFO 16-Bit Output Modes

- Cartesian to Polar Converter and Frequency Discriminator for AFC Loops and Demodulation of AM, FM, FSK, and DPSK

- Input Level Detector for External I.F. AGC Support

- Pb-Free Plus Anneal Available (RoHS Compliant)

製品比較

アプリケーション

- Single Channel Digital Software Radio Receivers

- Base Station Rx's: AMPS, NA TDMA, GSM, and CDMA

- Compatible with HSP50210 Digital Costas Loop for PSK Reception

- Evaluation Platform Available

ドキュメント

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| データシート | PDF 4.40 MB | |

| EOL通知 | PDF 1.17 MB | |

| EOL通知 | PDF 292 KB | |

| その他資料 | PDF 204 KB | |

| アプリケーションノート | PDF 375 KB | |

| アプリケーションノート | PDF 942 KB | |

6件

|

||

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

適用されたフィルター