概要

説明

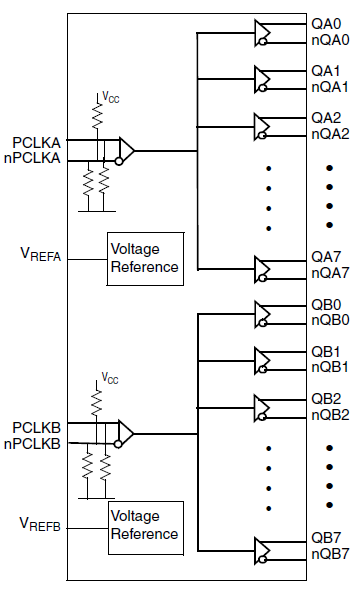

8SLVP2108Iは、高性能なデュアル差動 1:8 LVPECLファンアウトバッファです。 このデバイスは、高周波、超低加算位相ノイズのクロック信号やデータ信号のファンアウト用に設計されています。 8SLVP2108Iは、3.3Vまたは2.5Vの電源で動作するように最適化されています。 8SLVP2108Iは、出力間および部品間のスキュー特性を保証しており、明確な性能と再現性が要求されるクロック分配アプリケーションに理想的な製品です。8つの低スキュー出力を伴う2つの独立バッファが利用できます。 バイアス基準電圧を内蔵しているため、シングルエンド信号をデバイス入力に簡単に接続できます。このデバイスは、低消費電力と低加算位相ノイズが最適化されています。

特長

-

Two 1:8, low skew, low additive jitter LVPECL fanout buffers

-

Two differential clock inputs

-

Differential PCLKA, nPCLKA and PCLKB, nPCLKB pairs can accept the following differential input levels: LVDS, LVPECL, CML

-

Differential PCLKA, nPCLKA and PCLKB, nPCLKB pairs can also accept single-ended LVCMOS levels.

-

Maximum input clock frequency: 2GHz

-

Output bank skew: 15ps (typical)

-

Propagation delay: 390ps (maximum)

-

Low additive phase jitter, RMS: 54fs (maximum) (fREF = 156.25MHz, VPP = 1V, 12kHz – 20MHz, VCC = 3.3V)

-

Full 3.3V and 2.5V supply voltage

-

Maximum device current consumption (IEE): 143mA

-

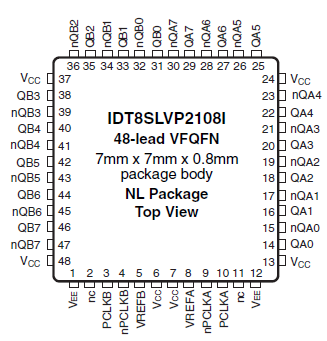

Available in Lead-free (RoHS 6), 48-Lead VFQFN package

-

-40°C to 85°C ambient operating temperature

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

適用されたフィルター

ビデオ&トレーニング

Description

Overview of IDT's 8LSVP (LVPECL) and 8SLVD (LVDS) families of low-jitter fanout buffers from IDT. Fanout buffers are a useful building block of many clock trees, providing signal buffering and multiple low-skew copies of the input signal. IDT's high-performance, low additive phase noise, differential clock fan-out buffers offer up to 2 GHz clock operation, low additive phase jitter (12kHz - 20MHz) of 50 to 100 femtoseconds RMS max, fast output rise & fall times (less than 150ps), and single and dual channel functions (dual: matched propagation delay). Presented by Baljit Chandhoke, Product Marketing Manager at Integrated Device Technology, Inc. To learn more about IDT's industry-leading portfolio of fanout buffers, visit Renesas's RF Buffer page.

Transcript