概要

説明

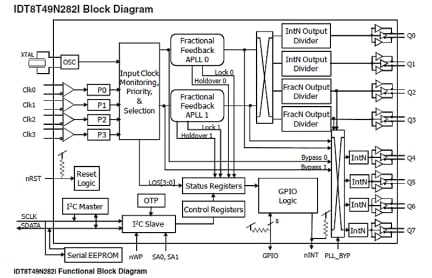

The 8T49N282I has two independent, fractional-feedback PLLs that can be used as jitter attenuators and frequency translators. It is equipped with six integer and two fractional output dividers, allowing the generation of up to eight different output frequencies, ranging from 8kHz to 1GHz. Four of these frequencies are completely independent of each other and the inputs. The other four are related frequencies. The eight outputs may select among LVPECL, LVDS, or LVCMOS output levels.

Renesas' third-generation Universal Frequency Translator family also includes the 8T49N281i (2-in/1-PLL/8-out) and the 8T49N283i (2-in/2-PLL/8-out).

To see other devices in this product family, visit the Universal Frequency Translators page.

特長

- Two differential outputs meet jitter limits for 100G Ethernet and STM-256/OC-768

- <0.3ps RMS (including spurs): 12kHz to 20MHz

- Accepts up to four LVPECL, LVDS, LVHSTL, HCSL, or LVCMOS input clocks ranging from 8kHz up to 875MHz

- Auto and manual input clock selection with hitless switching

- Clock input monitoring, including support for gapped clocks

- Phase-Slope Limiting and Fully Hitless Switching options to control output phase transients

- Operates from a 10MHz to 40MHz fundamental-mode crystal

- Generates eight LVPECL/LVDS or 16 LVCMOS output clocks ranging from 8kHz up to 1.0GHz (diff), 8kHz to 250MHz (LVCMOS)

- Register programmable through I2C/SPI or via external I2C EEPROM

- Supported by Renesas' Timing Commander™ software

製品比較

アプリケーション

- OTN or SONET/SDH equipment line cards (up to OC-192, and supporting FEC ratios)

- OTN de-mapping (Gapped Clock and DCO mode)

- Gigabit and Terabit IP switches/routers including support of Synchronous Ethernet

- Wireless base station baseband

- Data communications

設計・開発

ソフトウェア/ツール

ソフトウェア/ツール

| Software title

|

Software type

|

会社名

|

|---|---|---|

| Timing Commander Timing Commander™は、Windows™ベースの革新的なソフトウェアプラットフォームで、システム設計を行うエンジニアは、直感的かつ柔軟なグラフィカルユーザインタフェース(GUI)により、高度なタイミングデバイスの構成、プログラミング、モニタリングが行えます。

|

Code Generator | ルネサス |

1件

|

||

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

適用されたフィルター

ビデオ&トレーニング

Description

Transcript

ニュース&ブログ

| Benefits of a Point-of-Use Clock for Jitter Optimization | ブログ | 2021年4月27日 |