概要

説明

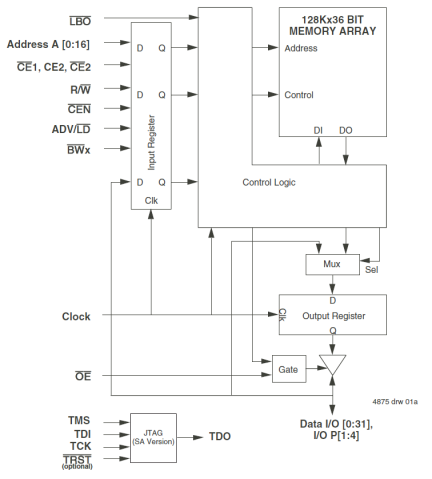

The 71V2556 3.3V CMOS synchronous SRAM, organized as 128K x 36, is designed to eliminate dead bus cycles when turning the bus around between reads and writes or writes and reads. Thus, it has been given the name ZBT™, or Zero Bus Turnaround. The 71V2556 contains data I/O, address, and control signal registers. It can provide four cycles of data for a single address presented to the SRAM.

特長

- High-performance system speed 166MHz (3.5ns Clock-to-Data access)

- ZBT feature - No dead cycles between write and read cycles

- Internally synchronized output buffer enable eliminates the need to control OE

- Single R/W (Read/Write) control pin

- Positive clock-edge triggered address, data, and control signal registers for fully pipelined applications

- 4-word burst capability (interleaved or linear)

- Individual byte write (BW1 - BW4) control (May tie active)

- Three chip enables for simple depth expansion

- 3.3V power supply (±5%), 2.5V I/O supply (VDDQ)

- Optional - Boundary Scan JTAG interface (IEEE 1149.1 complaint)

- Available in 100-pin TQFP and 119-pin BGA packages

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

適用されたフィルター