設計者の悩み

設計者は、機能を維持または強化しながらシステムコストを削減する方法を常に模索しています。 同時に、機能の拡張と製品サイクルの短縮に対する市場の要求は、さらなる課題を生み出しています。 これらの相反する要件のバランスをとるには、システム設計に対する革新的なアプローチが必要です。

コスト削減のための効果的な戦略の1つは、部品点数を減らし、よりコスト効率の高いICを使用してシステムアーキテクチャを簡素化することです。 ただし、どのような変更を行う場合でも、システムの機能は変わらないか、理想的には改善する必要があります。

システムコスト削減の課題

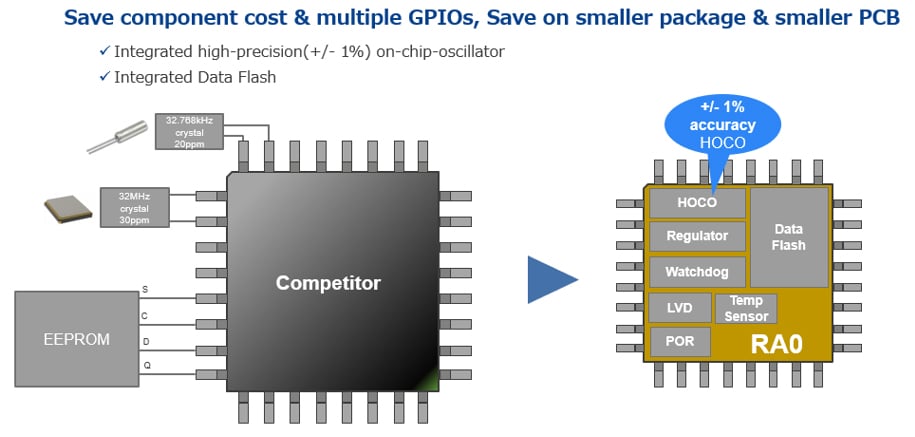

コストを最小限に抑えるための1つのアプローチは、外部発振器をオンチップ発振器に置き換えたり、外部EEPROMを組み込みデータフラッシュに置き換えたりするなど、外付け部品を排除することです。 これにより、部品点数と基板サイズの両方を減らすことで、システムコストを削減できます。 さらに、余分なピンが解放され、他の機能に再割り当てできます。

ただし、これらの最適化には技術的な課題があります。 たとえば、UART通信では、信頼性の高いデータ伝送を確保するために、通常、周波数誤差を2%から3%以内にする必要があります。 通信相手のデバイスに周波数誤差が2%ある場合、MCUは合計3%の制限内にとどまるために1%以下の誤差マージンを維持する必要があります。 ローエンドのマイコンにはこのような高精度な発振器が搭載されていないものが多く、データシートに仕様書が記載されている場合でも、チューニングのために外付け抵抗が必要になることがあります。 同様に、EEPROMのようなメモリが組み込まれたローエンドMCUは広く利用されていません。

RA0E2 MCUの利点

RA0E2 MCUは、これらの課題に効果的に対処します。 最大誤差±1%の高速発振器を内蔵しており、すべての動作温度(-40°C〜125°C)で保証されています。 さらに、データフラッシュが統合されているため、外部EEPROMが不要です。 これらの機能により、部品点数を減らすことができ、システムコストの削減と設計の簡素化につながります。 さらに、空いたピンはGPIOやその他の機能に利用できるため、同じパッケージサイズ内で柔軟性が向上します。

ラピッドプロトタイピング

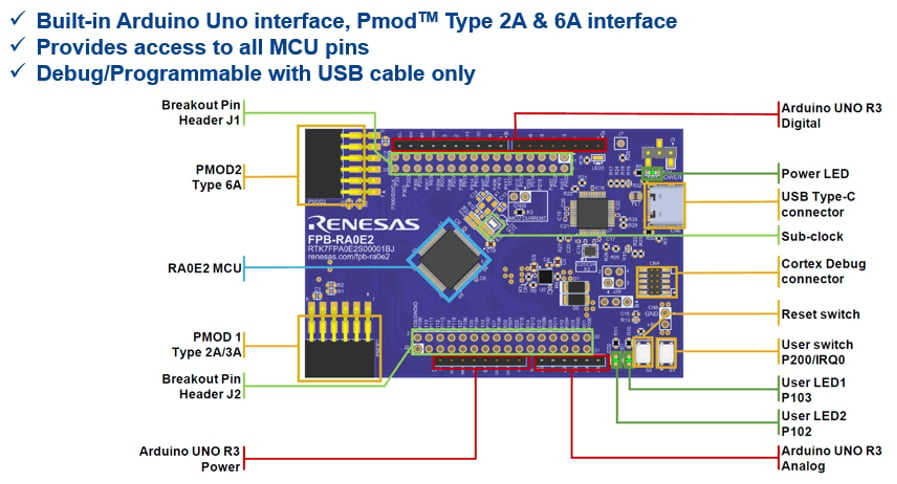

RA0E2 MCUの開発を加速するために、Fast Prototyping Board(FPB)が利用可能です。 この評価ボードは、評価プロセスを効率化し、設計者がプロトタイプ製品をより効率的に開発およびテストできるように設計されています。

まとめ

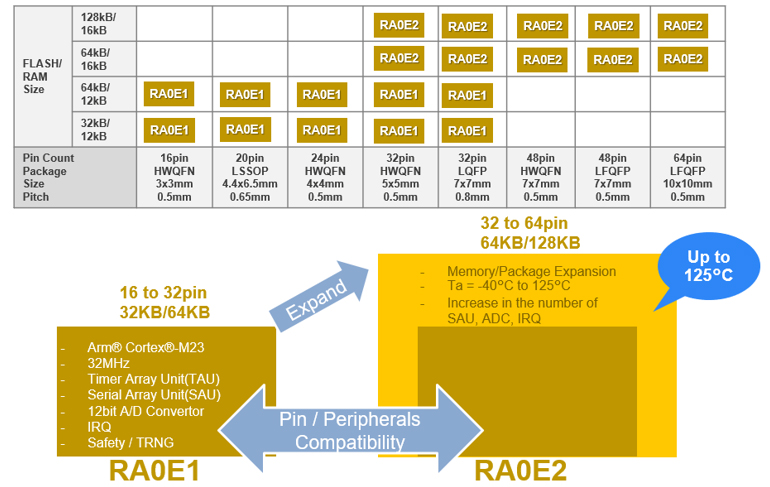

RA0E2 MCUシリーズは、設計者が性能を犠牲にすることなくコスト削減を達成するのに役立つ貴重な機能を提供します。 RA0シリーズは、先にリリースしたRA0E1シリーズと合わせて、ROMサイズ(32kB〜128kB)とピン数(16〜64ピン)を豊富に取り揃えており、多様なアプリケーションに適しています。 さらに、FPB-RA0E2評価ボードは、ラピッドプロトタイピングのための手頃な価格のソリューションを提供し、開発プロセスをさらに簡素化します。

RA0E1およびRA0E2の機能と利点の詳細については、 renesas.com/ra0e1 および renesas.com/ra0e2.

をご覧ください。評価ボードの詳細については、 renesas.com/fpb-ra0e2 をご覧ください。