概要

説明

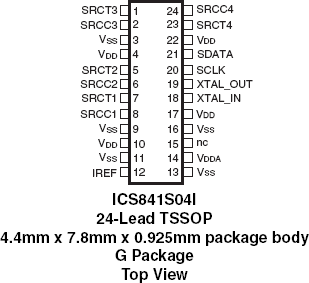

The 841S04I is a PLL-based clock generator specifically designed for PCI_Express™ Clock Generation applications. This device generates a 100MHz HCSL clock. The device offers a HCSL (Host Clock Signal Level) clock output from a clock input reference of 25MHz. The input reference may be derived from an external source or by the addition of a 25MHz crystal to the on-chip crystal oscillator. An external reference may be applied to the XTAL_IN pin with the XTAL_OUT pin left floating. The device offers spread spectrum clock output for reduced EMI applications. An I2C bus interface is used to enable or disable spread spectrum operation as well as select either a down spread value of -0.35% or -0.5%.

特長

- Four 0.7V current mode differential HCSL output pairs

- Crystal oscillator interface: 25MHz

- Output frequency: 100MHz

- RMS period jitter: 3ps (maximum)

- Output skew: 70ps (maximum)

- Cycle-to-cycle jitter: 35ps (maximum)

- I2C support with readback capabilities up to 400kHz

- Spread Spectrum for electromagnetic interference (EMI) reduction

- 3.3V operating supply mode

- -40°C to 85°C ambient operating temperature

- Available in lead-free (RoHS 6) package

製品比較

アプリケーション

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

適用されたフィルター

ビデオ&トレーニング

This is the first video in our PCIe series. In this video, we define PCIe architectures, focusing on common and separate clock architectures. Watch the rest of the video series below where Ron will cover the impact of different timing architectures.

Watch the Video Series Below