概要

説明

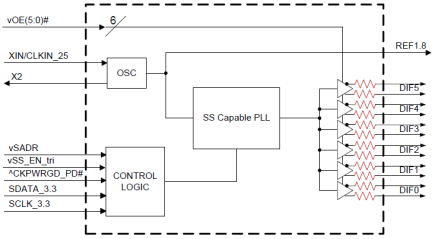

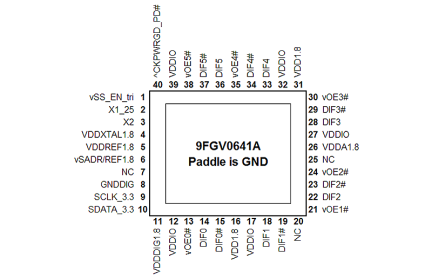

9FGV0641は、ルネサスのSOC対応 1.8V超低消費電PCIeクロックファミリーのひとつです。 このデバイスは100Ωの出力終端を内蔵しており、100Ωの伝送ラインに方向性を持たせて接続することができます。 また、クロック管理用に6つの出力イネーブルを備え、スペクトラム拡散オフに加えて2種類のスペクトラム拡散レベルにも対応しています。

評価ボードや材料に関する情報は、お近くの販売代理店にお問い合わせください。

特長

- PCIe Gen1-4準拠

- 終端内蔵LP-HCSL出力;標準的なPCIeデバイスと比較して24個の抵抗を節約可能

- 標準消費電力54mW;熱に関する懸念を低減

- 出力はオプションで1.05〜1.8Vの任意の電圧から出力可能;最大限の省電力を実現

- OE#ピン;DIFパワーマネージメント対応

- 各出力のプログラマブルスルー・レート;様々な線長に合わせたチューニングが可能

- プログラマブル出力振幅;様々な使用環境に合わせたチューニングが可能

- PLLがロックされるまでのDIF出力;クリーンなシステムスタートアップ

- 0%、-0.25%、-0.5%から選択可能なDIF出力スプレッド;EMIの低減

- 外付け25MHz水晶振動子、0ppmの合成エラーでタイトなppmをサポート

- ストラップピンによるコンフィギュレーションが可能;デバイス制御にSMBusインタフェースは不要

- 3.3 VトレラントSMBusインタフェースは、レガシーコントローラに対応

- 省スペースな5×5mm 40ピンVFQFPN;最小限の基板スペースを実現

- 選択可能なSMBusアドレス;複数のデバイスでSMBusセグメントを簡単に共有可能

製品比較

アプリケーション

設計・開発

ソフトウェア/ツール

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

適用されたフィルター

ビデオ&トレーニング

PCIe Reference Clock Jitter Budgets

Ron Wade, chief PCIe system architect explains the fundamental difference in reference clock jitter budgets between the first three generations of the specification and those of Gen4 and Gen5 which raise new challenges for designers.

Related Resources

Video List