概要

説明

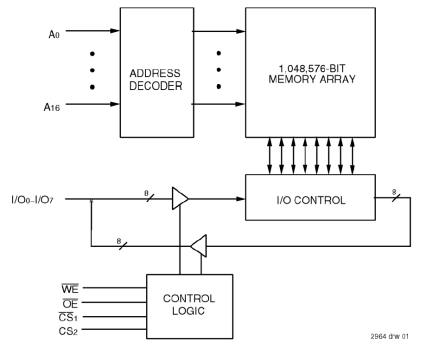

The 71024 5V CMOS SRAM is organized as 128K x 8. All bidirectional inputs and outputs of the 71024 are TTL-compatible, and operation is from a single 5V supply. Fully static asynchronous circuitry is used; no clocks or refreshes are required for operation.

特長

- Commercial (0C to +70C), Industrial (–40C to +85C)

- Equal access and cycle times — Commercial and Industrial: 12/15/20ns

- Two Chip Selects plus one Output Enable pin

- Bidirectional inputs and outputs directly TTL-compatible

- Low power consumption via chip deselect

- Available in 300 and 400 mil Plastic SOJ packages

製品比較

アプリケーション

ドキュメント

ピックアップ

ログイン後、ご登録が可能となります。

|

|

|

|

|---|---|---|

| 分類 | タイトル | 日時 |

| データシート | PDF 204 KB | |

| EOL通知 | PDF 768 KB | |

| ガイド | PDF 292 KB English | |

| ガイド | PDF 568 KB English | |

| ガイド | PDF 1.31 MB English | |

| EOL通知 | PDF 938 KB | |

| EOL通知 | PDF 909 KB | |

| 製品変更通知 | PDF 748 KB | |

| 製品変更通知 | PDF 108 KB | |

9件

|

||

設計・開発

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

適用されたフィルター