概要

説明

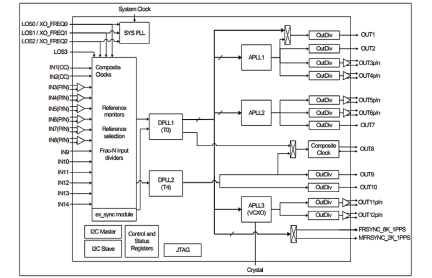

The 82P33731 Synchronous Equipment Timing Source (SETS) for 10G Synchronous Ethernet (SyncE) provides tools to manage timing references, clock generation and timing paths for SyncE based clocks, per ITU-T G.8264 and ITU-T G.8262. 82P33731 meets the requirements of ITU-T G.8262 for synchronous Ethernet Equipment Clocks (EECs) and ITU-T G.813 for Synchronous Equipment Clocks (SEC). The device outputs low-jitter clocks that can directly synchronize 40GBASE-R, 10GBASE-R and 10GBASE-W and lower-rate Ethernet interfaces; as well as CPRI/OBSAI, SONET/SDH and PDH interfaces. For 1G SyncE applications, see the 82P33714.

IDT’s third generation Universal Frequency Translator family also includes the 8T49N285 (2-in / 1-PLL / 8-out), 8T49N286 (4-in / 2-PLL / 8-out), 8T49N287 (2-in / 2-PLL / 8-out), and the 8T49N242 (2-in / 1-PLL / 4-out).

► Download the Altera and IDT Synchronous Ethernet Solution for ITU-T G.8262 white paper

特長

- Complies with ITU-T G.8262 for Synchronous Ethernet Equipment Clock (EEC), and G.813 for Synchronous Equipment Clock (SEC), and Telcordia GR-253-CORE for Stratum 3 and SONET Minimum Clock (SMC)

- DPLLs lock to a wide range of reference clock frequencies including: 10/100/1000 Ethernet, 10G Ethernet, OTN, SONET/SDH, PDH, TDM, GSM, CPRI/OBSAI and GNSS frequencies using fractional-N input dividers

- Generates clocks for: Ethernet, SONET/SDH and PDH interfaces: jitter generation <1 ps RMS (12 kHz to 20 MHz)

- Generates clocks for: 10GBASE-R, 10GBASE-W, 40GBASE-R and CPRI/OBSAI interfaces without external jitter attenuators: jitter generation <0.3 ps RMS (10 kHz to 20 MHz)

- Automatic reference selection state machines select the active reference for each DPLL based on the reference monitors, priority tables, revertive and non-revertive settings and other programmable settings

- Prevents output frequency corruption due to a bad PHY reference by accepting Loss of Signal (LOS) inputs from PHYs that immediately disqualify a reference

- DPLL1 can be configured as a DCO (Digitally Controlled Oscillator) to support IEEE 1588 based clock generation under external processor control

- Supports network timing master applications by locking to 1 PPS (Pulse Per Second) references from GPS or other GNSS sources

- Eases local oscillator sourcing by supporting any of eight common TCXO/OCXO frequencies for the System Clock: 10 MHz, 12.8 MHz, 13 MHz, 19.44 MHz, 20 MHz, 24.576 MHz, 25 MHz or 30.72 MHz

- Automatically loads configuration from an external EPROM after reset without processor intervention

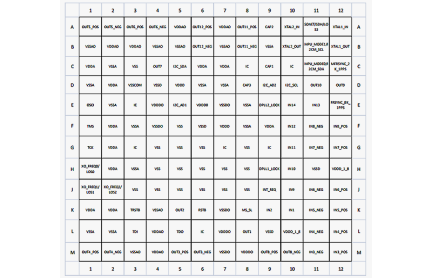

- 72 pin QFN package

製品比較

アプリケーション

設計・開発

ソフトウェア/ツール

ソフトウェア/ツール

| Software title

|

Software type

|

会社名

|

|---|---|---|

| Timing Commander Timing Commander™は、Windows™ベースの革新的なソフトウェアプラットフォームで、システム設計を行うエンジニアは、直感的かつ柔軟なグラフィカルユーザインタフェース(GUI)により、高度なタイミングデバイスの構成、プログラミング、モニタリングが行えます。

|

Code Generator | ルネサス |

1件

|

||

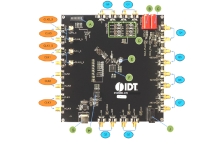

ボード&キット

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

適用されたフィルター

ビデオ&トレーニング

ニュース&ブログ

| A Reference Design Saved My Bacon | ブログ | 2018年4月27日 |

| IDT Introduces Synchronous Ethernet Solution for 4G/5G Mobile Networks Using Marvell PHYs | ニュース | 2018年4月26日 |