概要

説明

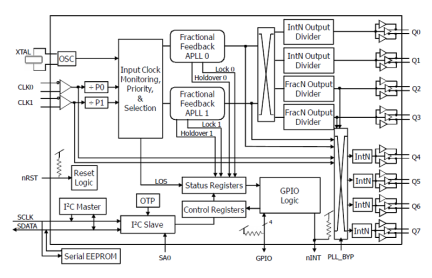

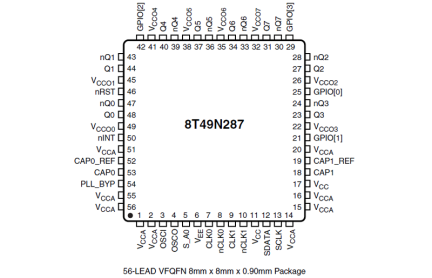

8T49N287は、フラクショナルフィードバックPLLを2つ搭載しており、ジッタ減衰を伴う周波数トランスレータや周波数シンセサイザとして使用することが可能です。 6つの整数、2つの分数出力分周器を搭載し、8kHz~1GHzの範囲で最大8種類の出力周波数を生成することが可能です。 出力周波数は入力周波数から完全に独立させることができ、これら最大4つの周波数はすべて互いに完全に独立させることができます。 8つの出力は、LVPECL、LVDS、HCSL、LVCMOSから出力レベルを選択することができます。

8T49N287は、10G/40G/100G SONET/SDHおよびイーサネットネットワークラインカード、無線基地局ベースバンドユニット、ビデオ放送、キャリアイーサネット・スイッチ、OTN、またはテストおよび測定アプリケーションなどの幅広い機器での使用に最適です。 8T49N287は、GbE/10GbE/100GbE 同期イーサネット ラインカードアプリケーションで、タイミングカード上のSETS(イミング ソース同期装置)においてG.8262に準拠するために使用することができます。

ルネサスの第3世代ユニバーサル周波数トランスレータ・ファミリには、8T49N285(2入力/1PLL/8出力)、8T49N286(4入力/2PLL/8出力)、8T49N242(2入力/1PLL/4出力)も含まれています。 これらのデバイスは、同期イーサネット(SyncE)用の82P33714と10G-40G SyncE用の82P33731タイミングソース同期装置(SETS)で補完されます。

この製品ファミリの他のデバイスを参照する際、ユニバーサル周波数トランスレータのページをご覧ください。

特長

- Supports GR.1244 Stratum 3 stability in holdover mode

- Compliant with the requirements outlined in Telcordia GR-253-CORE (SONET) & ITU-T G.813/G.8262 (SDH/SONET & SyncE) when paired with a Synchronous Equipment Timing Source (SETS ) device

- Generates up to 8 LVPECL / LVDS/HCSL or 16 LVCMOS output clocks ranging from 8kHz up to 1.0 GHz (diff), 8 kHz to 250 MHz (LVCMOS), that meet jitter limits for 10G up to 100G Ethernet and STM-256/OC-768 applications

- 0.3ps RMS (including spurs), 12 kHz to 20 MHz

- Accepts up to two LVPECL, LVDS, LVHSTL, HCSL or LVCMOS input clocks ranging from 8 kHz up to 875 MHz

- Auto and manual input clock selection with hitless switching

- Clock input monitoring, including support for gapped clocks

- Phase-Slope Limiting and Fully Hitless Switching options to control output phase transients

- Operates from a 10 MHz to 40 MHz fundamental-mode crystal

- Register programmable through I2C / SPI or via external I2C EEPROM

- 8T49N287-993 “Boot from EEPROM”

- 8T49N287-994 “powers up disabled”

- Supported by Timing Commander Software

製品比較

アプリケーション

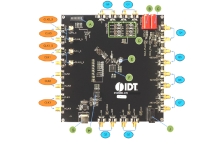

設計・開発

ソフトウェア/ツール

ソフトウェア/ツール

| Software title

|

Software type

|

会社名

|

|---|---|---|

| Timing Commander Timing Commander™は、Windows™ベースの革新的なソフトウェアプラットフォームで、システム設計を行うエンジニアは、直感的かつ柔軟なグラフィカルユーザインタフェース(GUI)により、高度なタイミングデバイスの構成、プログラミング、モニタリングが行えます。

|

Code Generator | ルネサス |

1件

|

||

ボード&キット

モデル

ECADモデル

[製品選択]テーブル内の製品名をクリックするとSamacSysが提供する回路図シンボル、PCBフットプリント、3D CADモデルがご確認いただけます。 お探しのシンボルやモデルが見つからない場合、Webサイトから直接リクエストできます。

製品選択

適用されたフィルター

ビデオ&トレーニング

Description

Transcript

ニュース&ブログ

| Benefits of a Point-of-Use Clock for Jitter Optimization | ブログ | 2021年4月27日 |